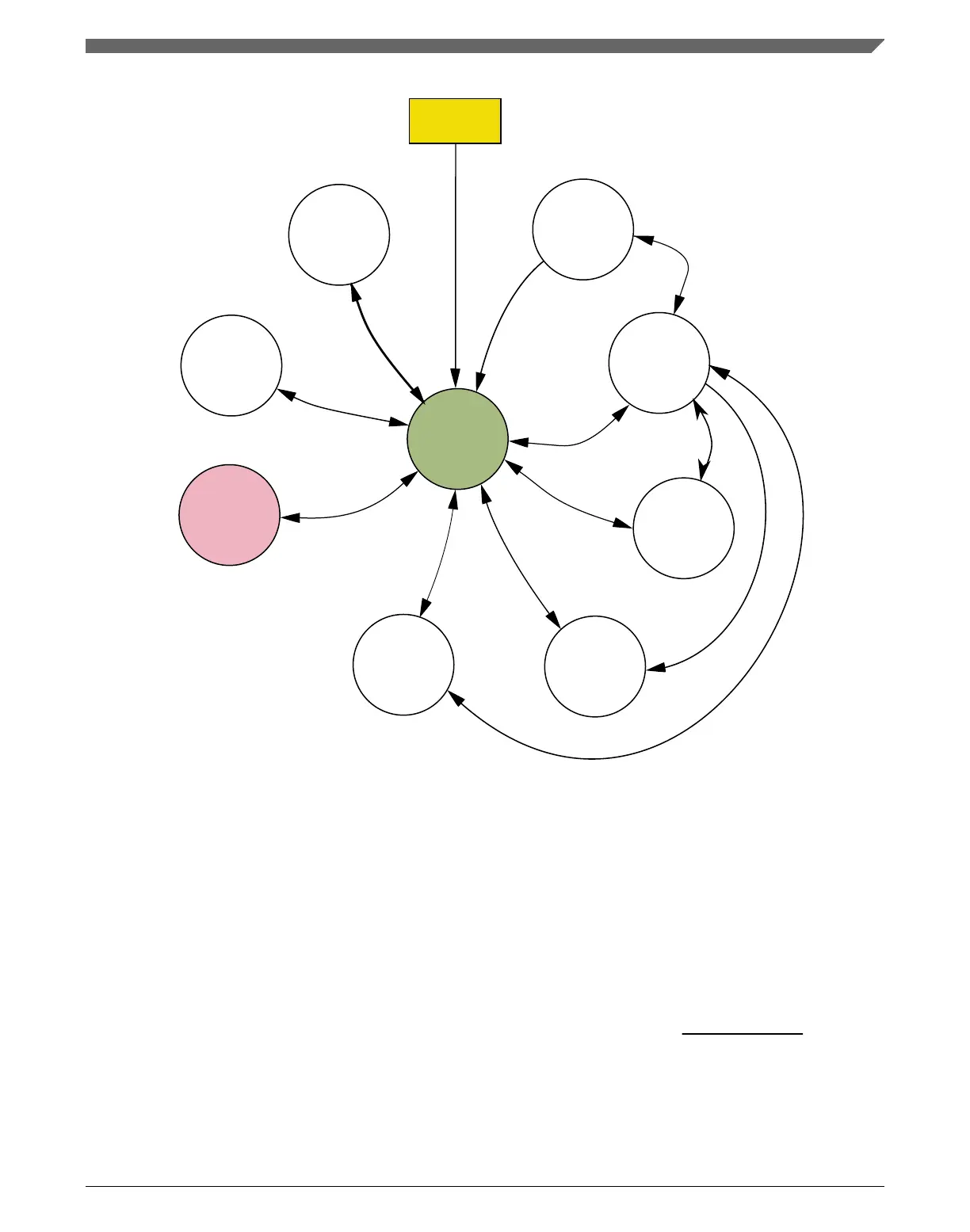

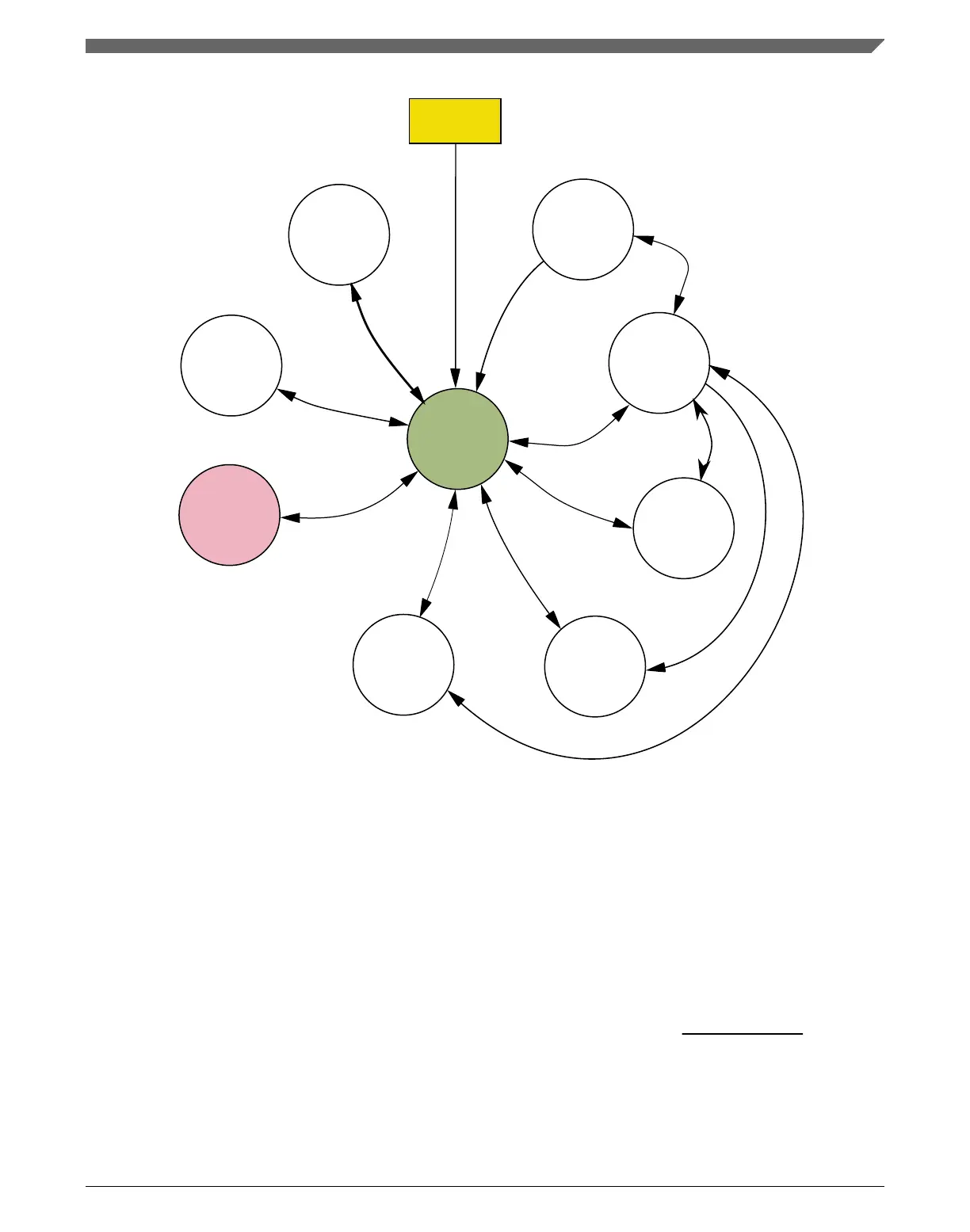

WAIT

STOP

RUN

LLS

VLLS

VLPS

VLPR

VLPW

Any RESET

HSRUN

4

6

7

3

1

2

8

10

11

9

5

12

Figure 7-1. Power mode state transition diagram

7.6

Power modes shutdown sequencing

When entering stop or other low-power modes, the clocks are shut off in an orderly

sequence to safely place the chip in the targeted low-power state. All low-power entry

sequences are initiated by the core executing an WFI instruction. The ARM core's

outputs, SLEEPDEEP and SLEEPING, trigger entry to the various low-power modes:

• System level wait and VLPW modes equate to: SLEEPING &

SLEEPDEEP

• All other low power modes equate to: SLEEPING & SLEEPDEEP

When entering the non-wait modes, the chip performs the following sequence:

Chapter 7 Power Management

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 189

Loading...

Loading...