23.1.2.2 Wait Mode

The EWM module treats the stop and wait modes as the same. EWM functionality

remains the same in both of these modes.

23.1.2.3 Debug Mode

Entry to debug mode has no effect on the EWM.

• If the EWM is enabled prior to entry of debug mode, it remains enabled.

• If the EWM is disabled prior to entry of debug mode, it remains disabled.

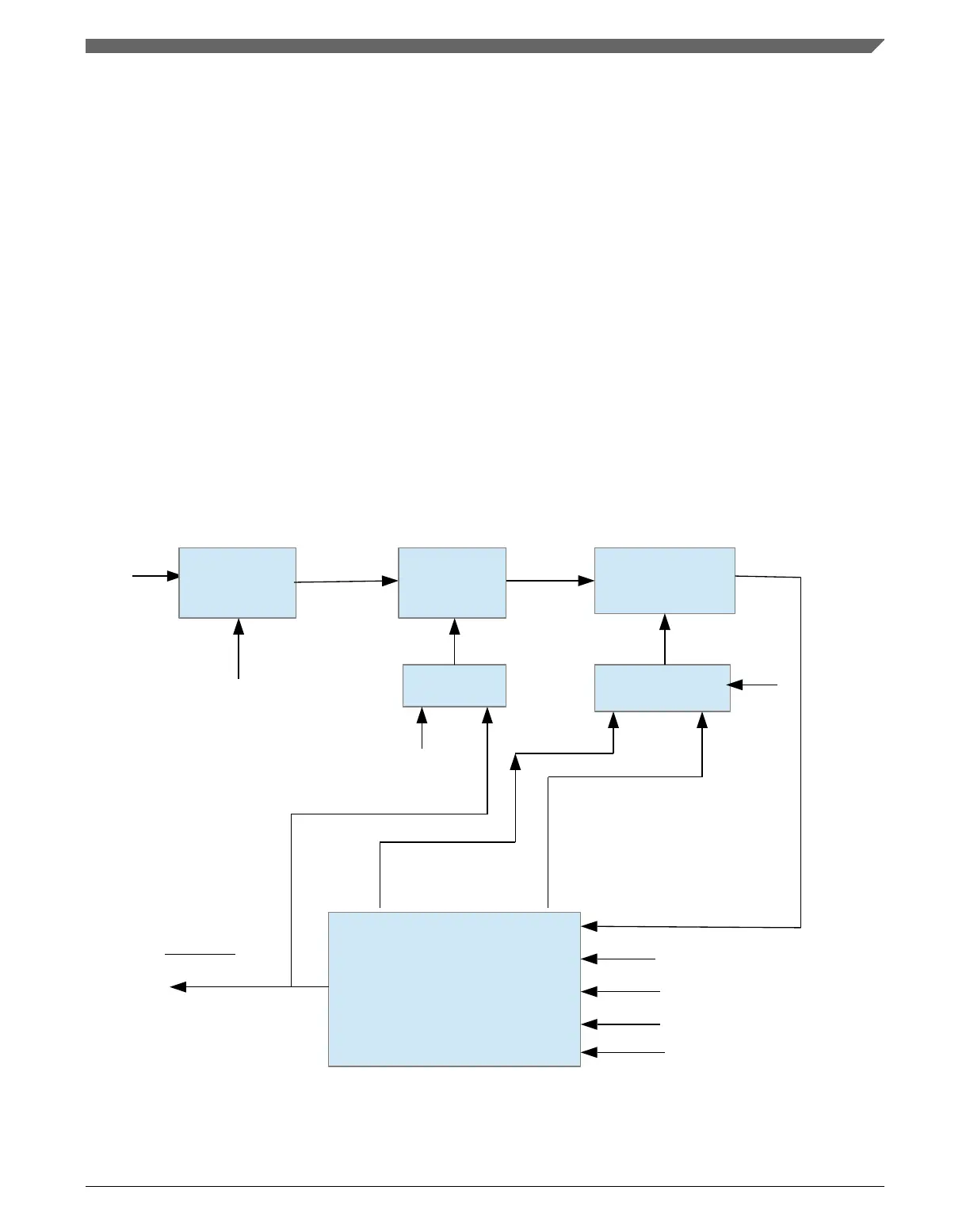

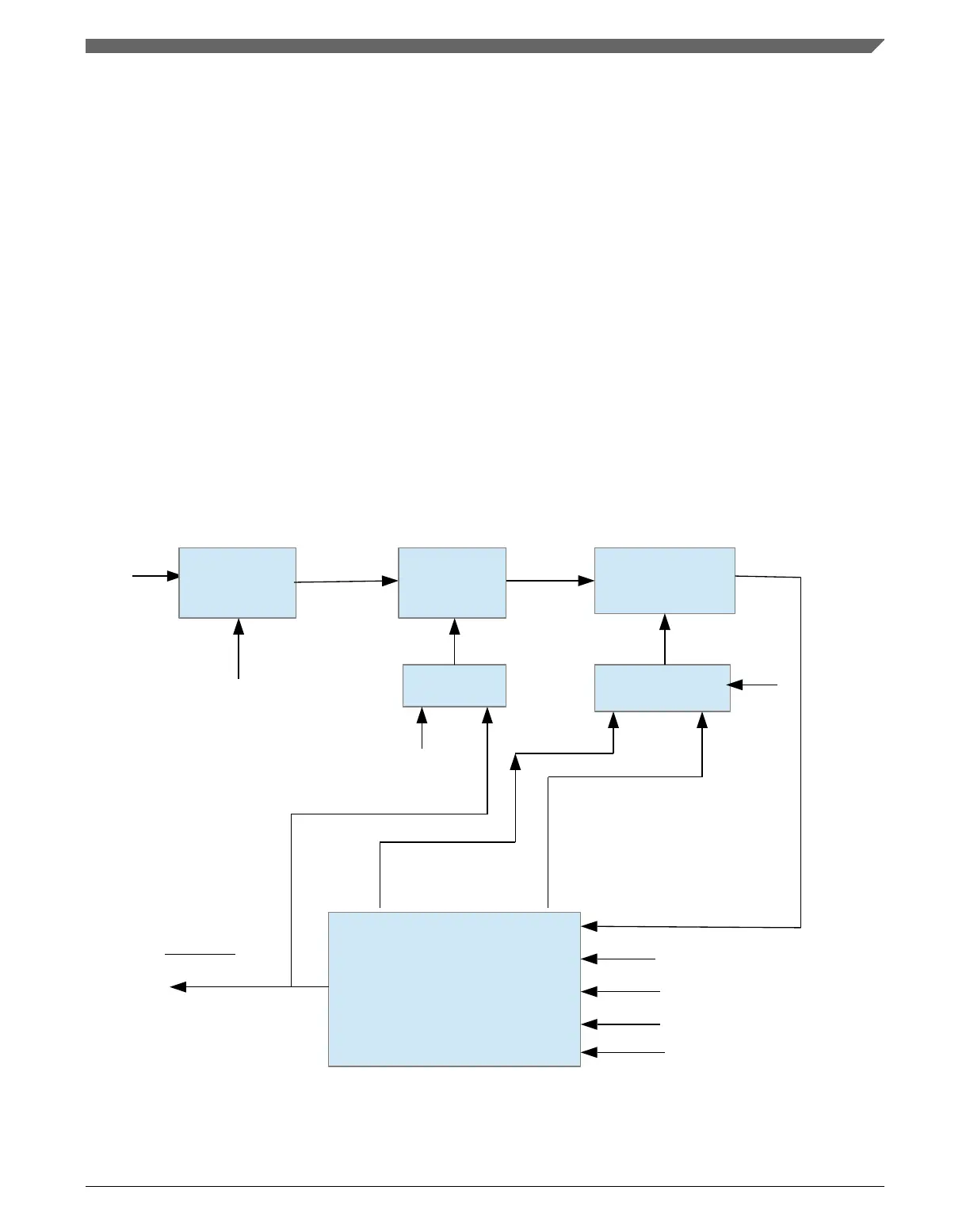

23.1.3

Block Diagram

This figure shows the EWM block diagram.

Clock Divider

Logic

LPO_CLK

Low Power

Clock

Clock Gating

Cell

AND

Enable

EWM_CTRL[EWMEN]

EWM_CLKPRESCALER[CLK_DIV]

8-bit Counter

OR

Counter Value

Reset to

Counter

EWM Refresh

And

/EWM_out Output

Control

Mechanism

EWM_CMPH[COMPAREH]

EWM_CMPL[COMPAREL]

EWM Refreshed

EWM_out

Counter

overflow

EWM_in

EWM Service Register

CPU

Reset

Figure 23-1. EWM Block Diagram

Chapter 23 External Watchdog Monitor (EWM)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 511

Loading...

Loading...