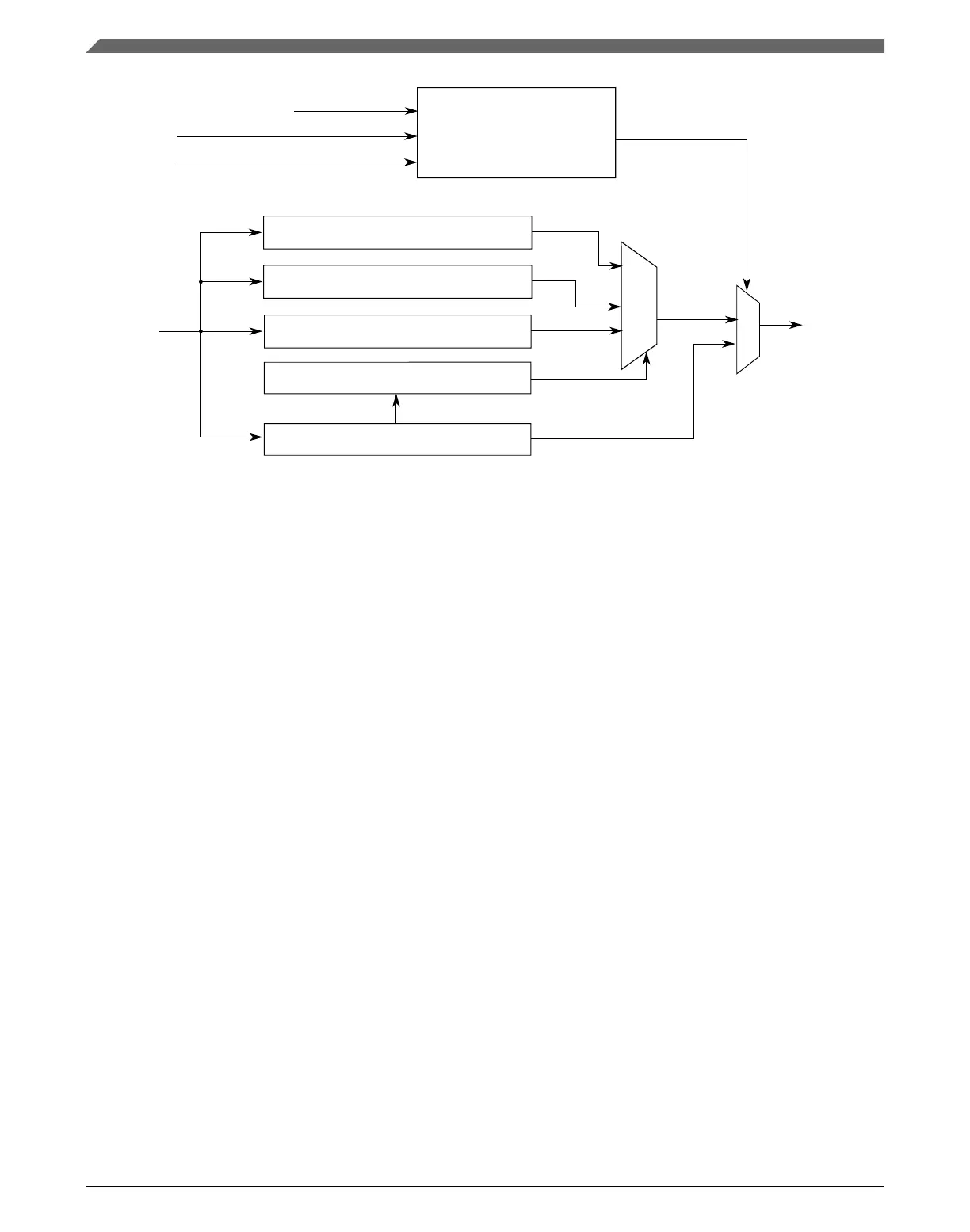

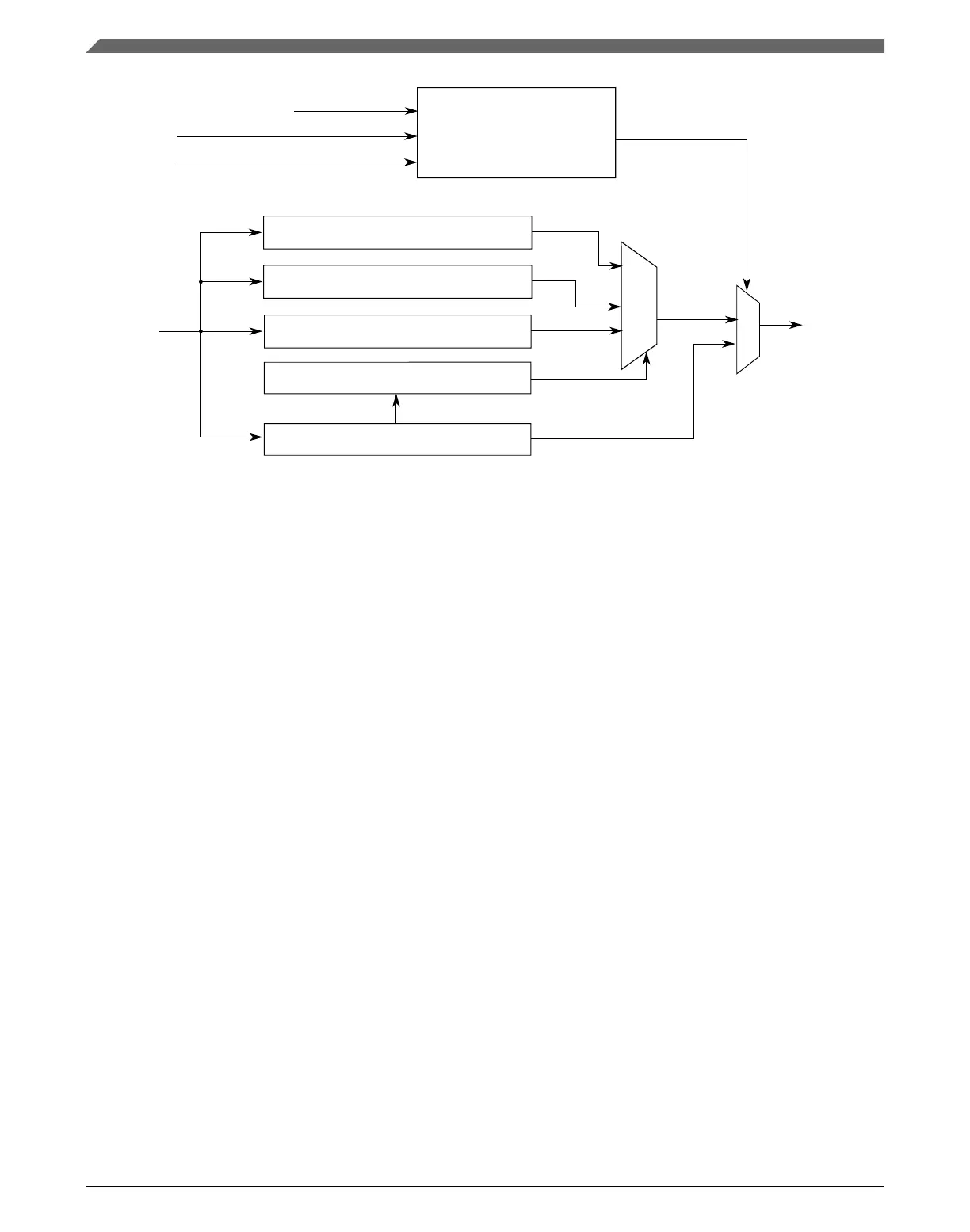

Power-on reset

TMS

TCK

TDI

1-bit Bypass Register

32-bit Device Identification Register

Boundary Scan Register

TAP Instruction Decoder

TAP Instruction Register

TDO

Test Access Port (TAP)

Controller

Figure 51-1. JTAG (IEEE 1149.1) block diagram

51.1.2

Features

The JTAGC block is compliant with the IEEE 1149.1-2001 standard, and supports the

following features:

• IEEE 1149.1-2001 Test Access Port (TAP) interface

• 4 pins (TDI, TMS, TCK, and TDO)

• Instruction register that supports several IEEE 1149.1-2001 defined instructions as

well as several public and private device-specific instructions. Refer to Table 51-3

for a list of supported instructions.

• Bypass register, boundary scan register, and device identification register.

• TAP controller state machine that controls the operation of the data registers,

instruction register and associated circuitry.

51.1.3

Modes of operation

The JTAGC block uses a power-on reset indication as its primary reset signals. Several

IEEE 1149.1-2001 defined test modes are supported, as well as a bypass mode.

Introduction

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1384 NXP Semiconductors

Loading...

Loading...