49.3.10 SAI Receive Control Register (I2Sx_RCSR)

Address: 4002_F000h base + 80h offset = 4002_F080h

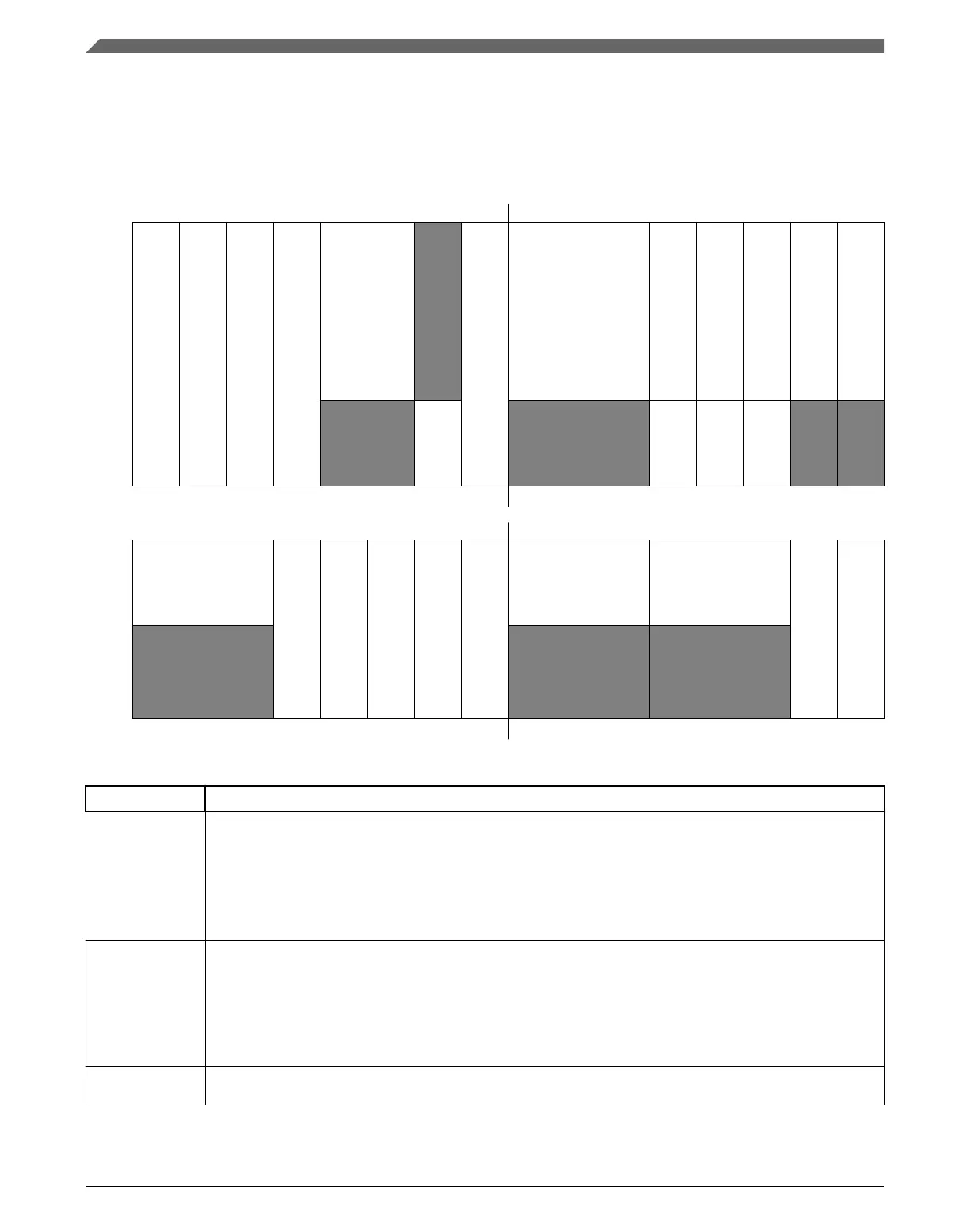

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

RE

STOPE

DBGE

BCE

0 0

SR

0

WSF

SEF FEF

FWF

FRF

W

FR w1c w1c w1c

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

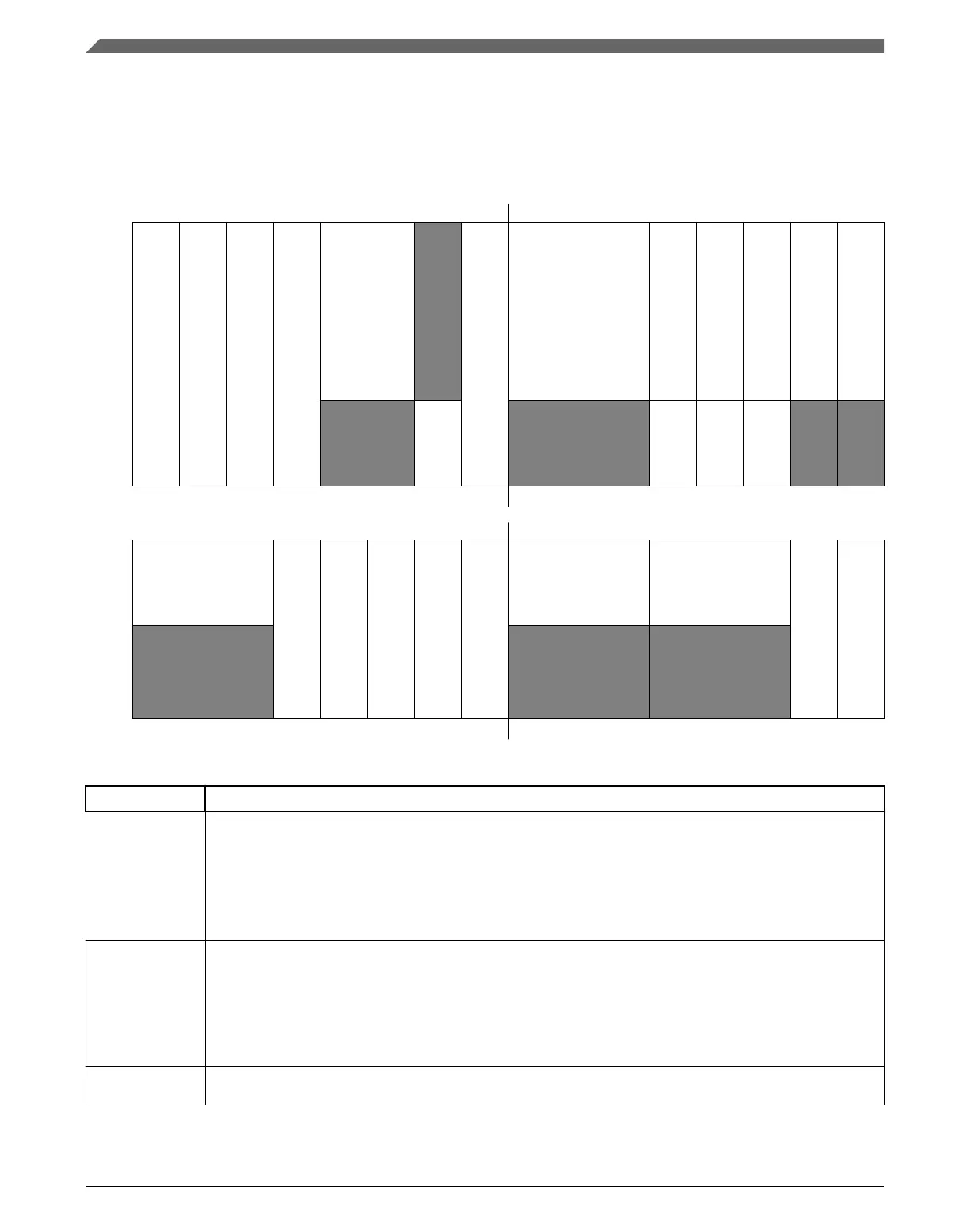

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

WSIE SEIE FEIE FWIE FRIE

0 0

FWDE

FRDE

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

I2Sx_RCSR field descriptions

Field Description

31

RE

Receiver Enable

Enables/disables the receiver. When software clears this field, the receiver remains enabled, and this bit

remains set, until the end of the current frame.

0 Receiver is disabled.

1 Receiver is enabled, or receiver has been disabled and has not yet reached end of frame.

30

STOPE

Stop Enable

Configures receiver operation in Stop mode. This bit is ignored and the receiver is disabled in all low-

leakage stop modes.

0 Receiver disabled in Stop mode.

1 Receiver enabled in Stop mode.

29

DBGE

Debug Enable

Table continues on the next page...

Memory map and register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1352 NXP Semiconductors

Loading...

Loading...