Table 10-1. Reference links to related information (continued)

Topic Related module Reference

Clocking Clock Distribution

Register access Peripheral bus

controller

Peripheral bridge

10.2.1 Port control and interrupt module features

• 32-pin ports

NOTE

Not all pins are available on the device. See the following

section for details.

• Each 32-pin port is assigned one interrupt.

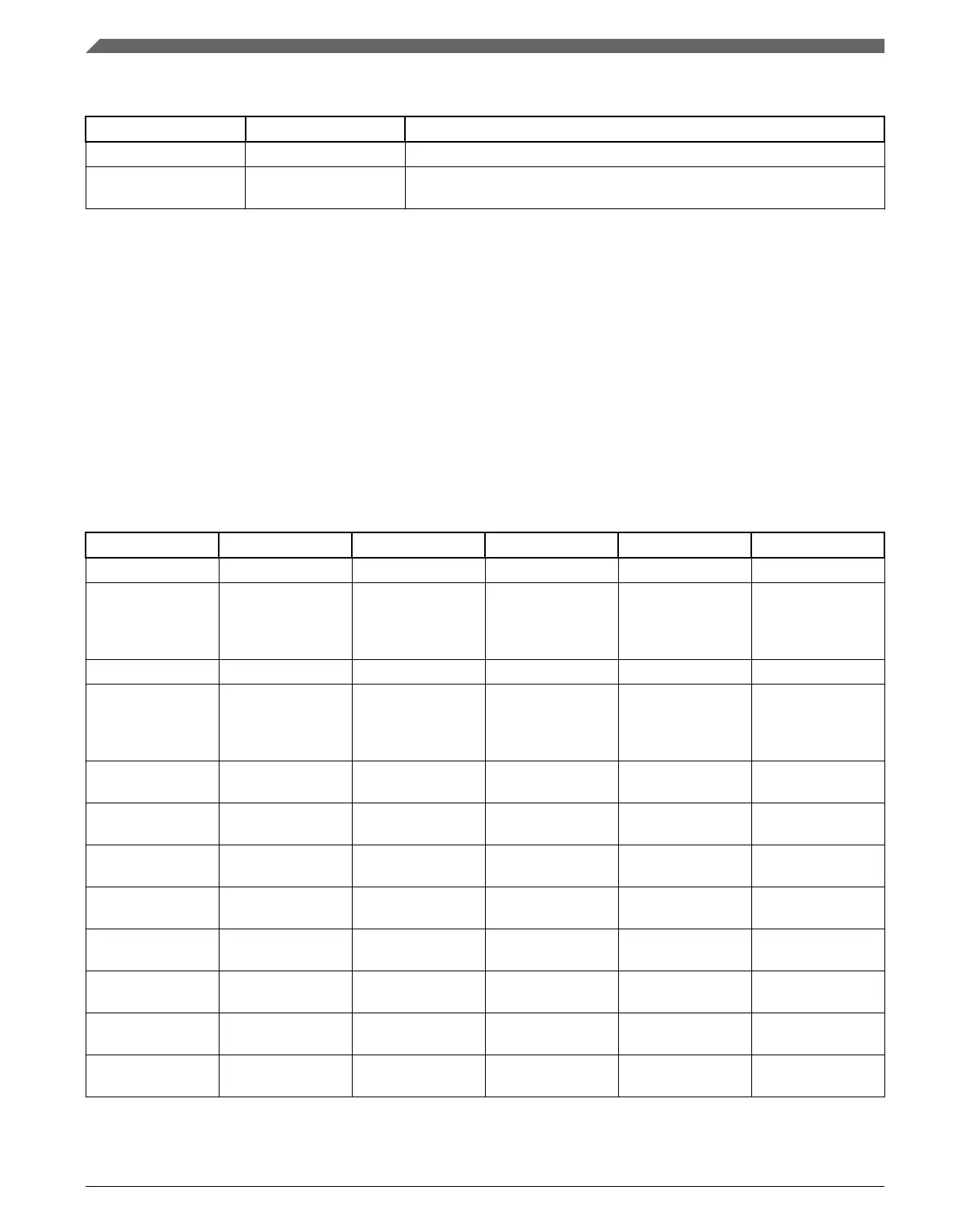

Table 10-2. Ports summary

Feature Port A Port B Port C Port D Port E

Pull select control Yes Yes Yes Yes Yes

Pull select at reset PTA1/PTA2/PTA3/

PTA4/PTA5=Pull

up, Others=Pull

down

Pull down Pull down Pull down Pull down

Pull enable control Yes Yes Yes Yes Yes

Pull enable at reset PTA0/PTA1/PTA2/

PTA3/

PTA4=Enabled;

Others=Disabled

Disabled Disabled Disabled Disabled

Slew rate enable

control

Yes Yes Yes Yes Yes

Slew rate enable at

reset

Disabled Disabled Disabled Disabled Disabled

Passive filter

enable control

PTA4=Yes;

Others=No

No No No No

Passive filter

enable at reset

Disabled Disabled Disabled Disabled Disabled

Open drain enable

control

Yes Yes Yes Yes Yes

Open drain enable

at reset

Disabled Disabled Disabled Disabled Disabled

Drive strength

enable control

No PTB0/PTB1 only PTC3/PTC4 only PTD4/PTD5/PTD6/

PTD7 only

No

Drive strength

enable at reset

Disabled Disabled Disabled Disabled Disabled

Table continues on the next page...

Signal Multiplexing Integration

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

214 NXP Semiconductors

Loading...

Loading...