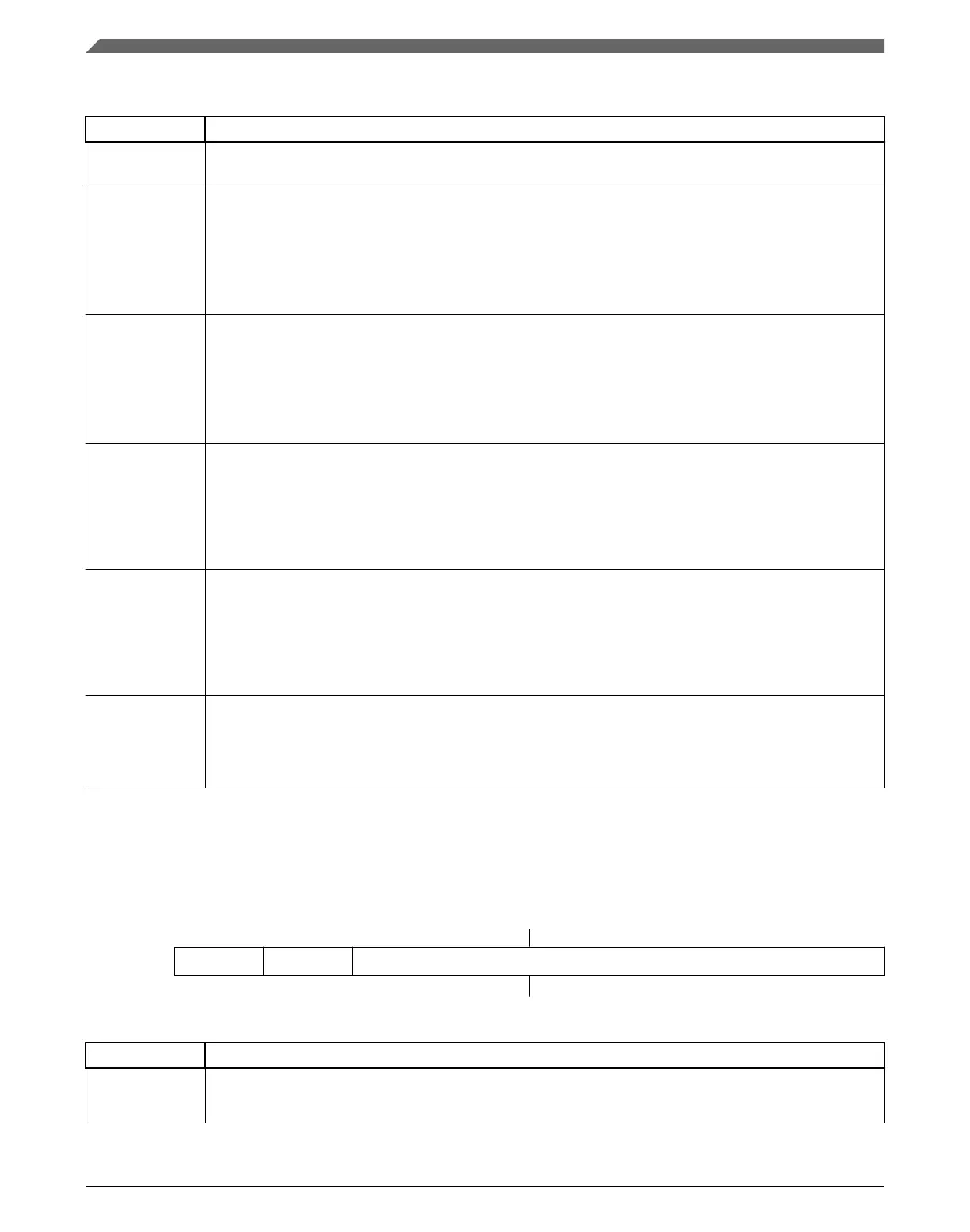

CMPx_SCR field descriptions (continued)

Field Description

5

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

4

IER

Comparator Interrupt Enable Rising

Enables the CFR interrupt from the CMP. When this field is set, an interrupt will be asserted when CFR is

set.

0 Interrupt is disabled.

1 Interrupt is enabled.

3

IEF

Comparator Interrupt Enable Falling

Enables the CFF interrupt from the CMP. When this field is set, an interrupt will be asserted when CFF is

set.

0 Interrupt is disabled.

1 Interrupt is enabled.

2

CFR

Analog Comparator Flag Rising

Detects a rising-edge on COUT, when set, during normal operation. CFR is cleared by writing 1 to it.

During Stop modes, CFR is edge sensitive .

0 Rising-edge on COUT has not been detected.

1 Rising-edge on COUT has occurred.

1

CFF

Analog Comparator Flag Falling

Detects a falling-edge on COUT, when set, during normal operation. CFF is cleared by writing 1 to it.

During Stop modes, CFF is edge sensitive .

0 Falling-edge on COUT has not been detected.

1 Falling-edge on COUT has occurred.

0

COUT

Analog Comparator Output

Returns the current value of the Analog Comparator output, when read. The field is reset to 0 and will read

as CR1[INV] when the Analog Comparator module is disabled, that is, when CR1[EN] = 0. Writes to this

field are ignored.

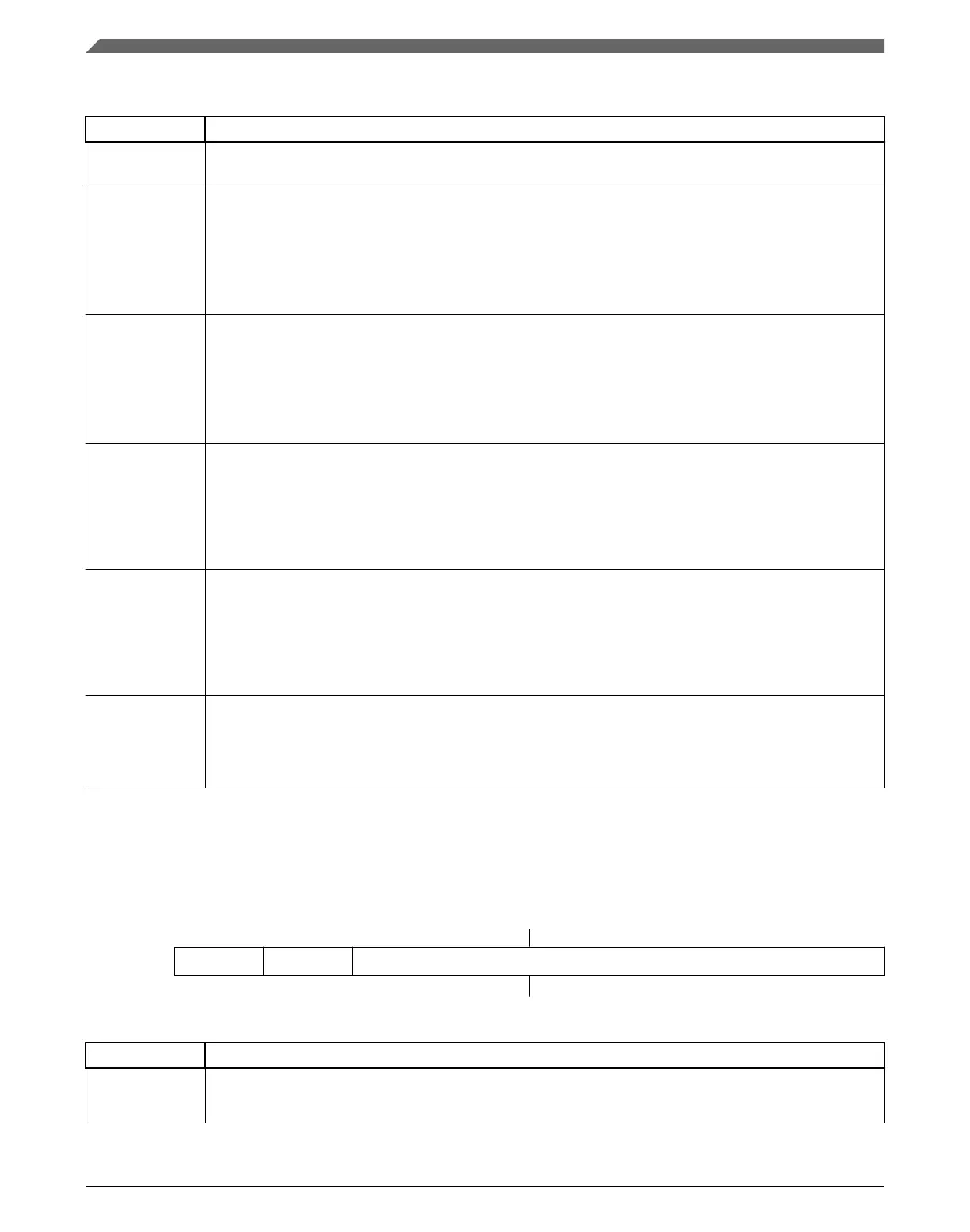

35.2.5 DAC Control Register (CMPx_DACCR)

Address: Base address + 4h offset

Bit 7 6 5 4 3 2 1 0

Read

DACEN VRSEL VOSEL

Write

Reset

0 0 0 0 0 0 0 0

CMPx_DACCR field descriptions

Field Description

7

DACEN

DAC Enable

Enables the DAC. When the DAC is disabled, it is powered down to conserve power.

Table continues on the next page...

Memory map/register definitions

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

826 NXP Semiconductors

Loading...

Loading...