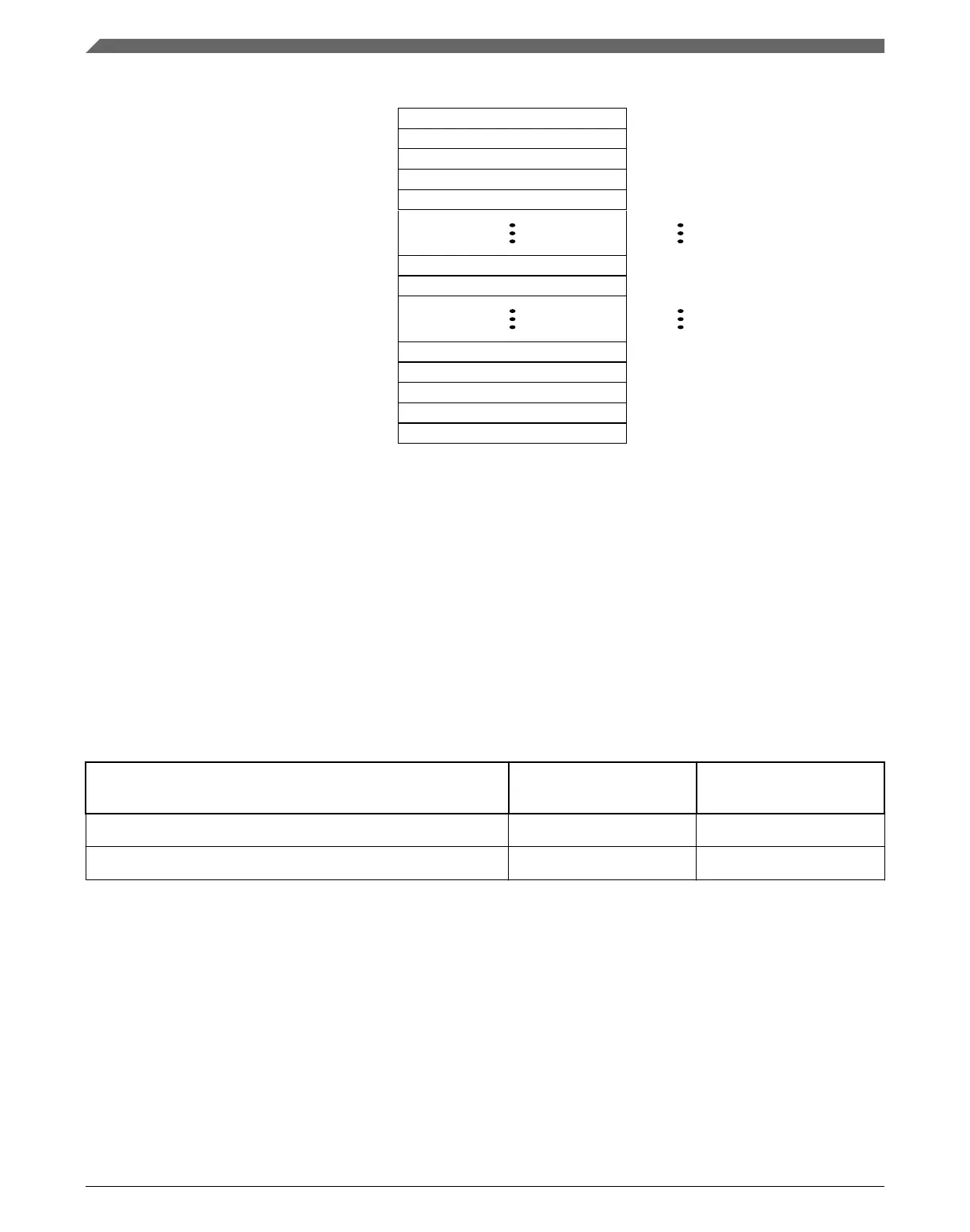

Program flash size / 64

SACCL3[SA0]

0x0_0000

Program flash

Last program flash address

Program flash size / 64

SACCL3[SA1]

Program flash size / 64

SACCL3[SA2]

Program flash size / 64

SACCL3[SA3]

Program flash size / 64

SACCL3[SA4]

Program flash size / 64

SACCL0[SA31]

Program flash size / 64

SACCH3[SA32]

Program flash size / 64

SACCH0[SA59]

Program flash size / 64

SACCH0[SA60]

Program flash size / 64

SACCH0[SA61]

Program flash size / 64

SACCH0[SA62]

Program flash size / 64

SACCH0[SA63]

Figure 29-4. Program flash supervisor access control (256KB or 512KB of program

flash)

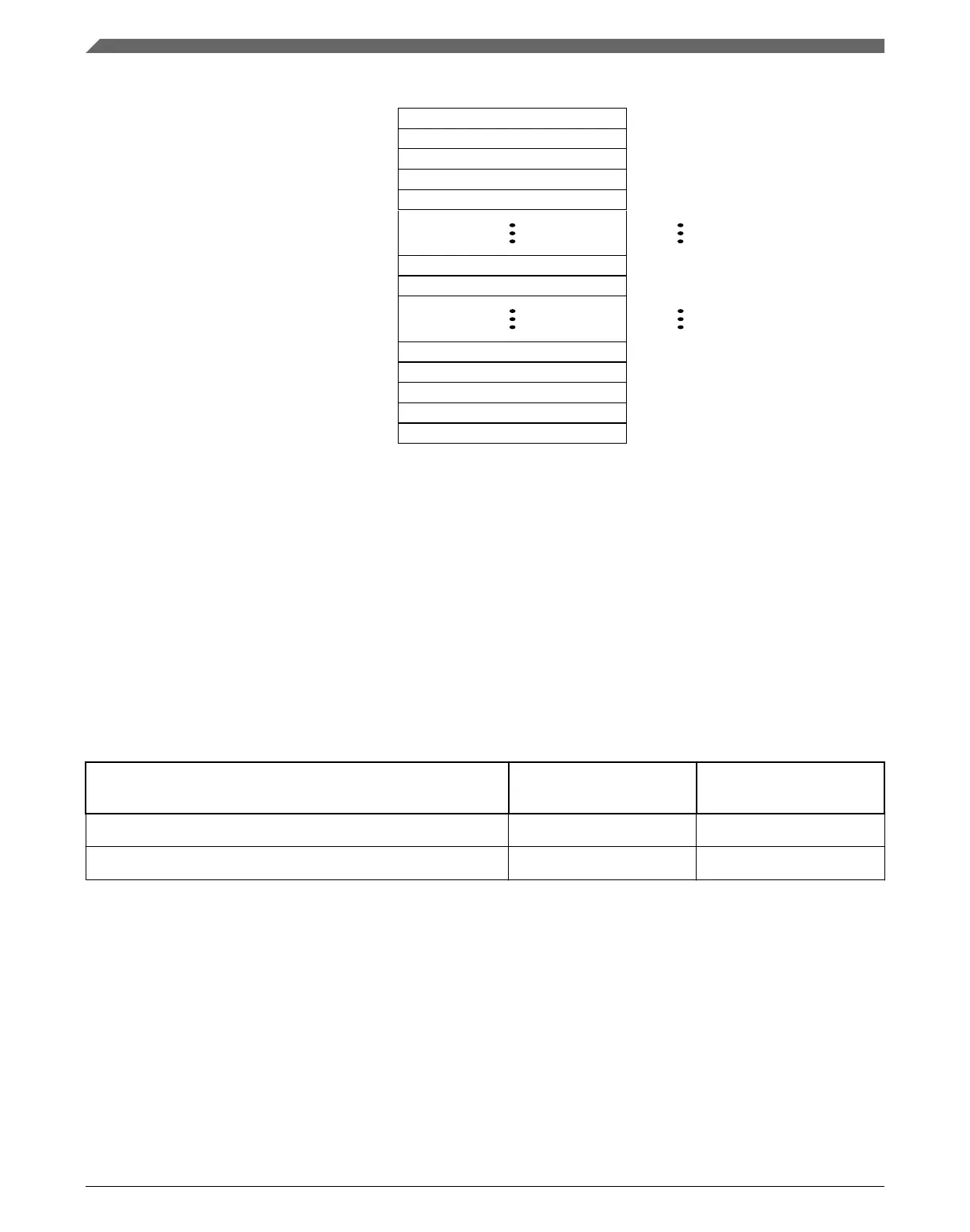

29.4.3

Interrupts

The flash memory module can generate interrupt requests to the MCU upon the

occurrence of various flash events.

These interrupt events and their associated status and control bits are shown in the

following table.

Table 29-1. Flash Interrupt Sources

Flash Event Readable

Status Bit

Interrupt

Enable Bit

Flash Command Complete FSTAT[CCIF] FCNFG[CCIE]

Flash Read Collision Error FSTAT[RDCOLERR] FCNFG[RDCOLLIE]

Note

Vector addresses and their relative interrupt priority are

determined at the MCU level.

Some devices also generate a bus error response as a result of a Read Collision Error

event. See the chip configuration information to determine if a bus error response is also

supported.

Functional Description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

650 NXP Semiconductors

Loading...

Loading...