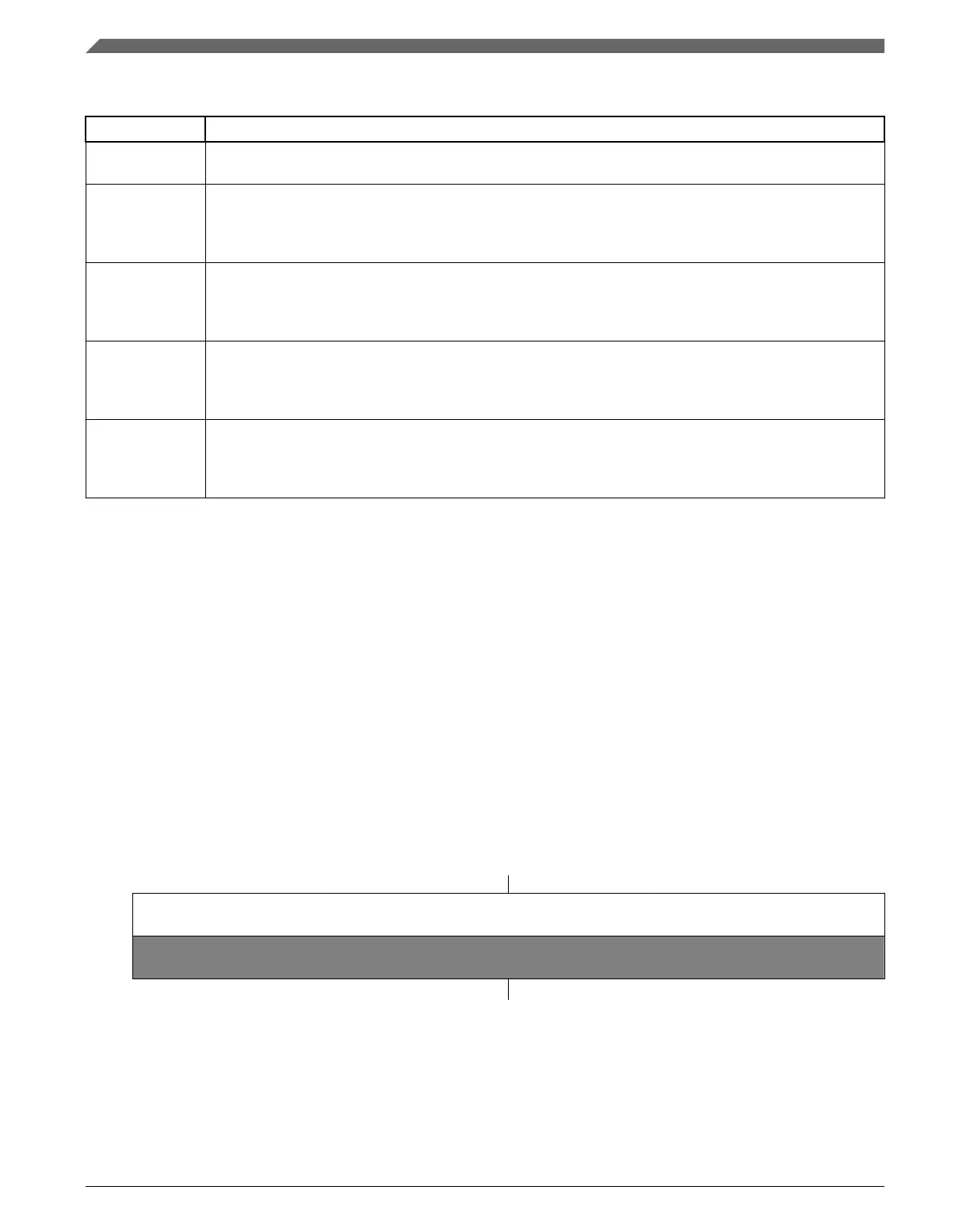

DMA_ERQ field descriptions (continued)

Field Description

0 The DMA request signal for the corresponding channel is disabled

1 The DMA request signal for the corresponding channel is enabled

3

ERQ3

Enable DMA Request 3

0 The DMA request signal for the corresponding channel is disabled

1 The DMA request signal for the corresponding channel is enabled

2

ERQ2

Enable DMA Request 2

0 The DMA request signal for the corresponding channel is disabled

1 The DMA request signal for the corresponding channel is enabled

1

ERQ1

Enable DMA Request 1

0 The DMA request signal for the corresponding channel is disabled

1 The DMA request signal for the corresponding channel is enabled

0

ERQ0

Enable DMA Request 0

0 The DMA request signal for the corresponding channel is disabled

1 The DMA request signal for the corresponding channel is enabled

22.3.8 Enable Error Interrupt Register (DMA_EEI)

The EEI register provides a bit map for the 16 channels to enable the error interrupt

signal for each channel. The state of any given channel’s error interrupt enable is directly

affected by writes to this register; it is also affected by writes to the SEEI and CEEI.

These registers are provided so that the error interrupt enable for a single channel can

easily be modified without the need to perform a read-modify-write sequence to the EEI

register.

The DMA error indicator and the error interrupt enable flag must be asserted before an

error interrupt request for a given channel is asserted to the interrupt controller.

Address:

4000_8000h base + 14h offset = 4000_8014h

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Memory map/register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

448 NXP Semiconductors

Loading...

Loading...