UARTx_RWFIFO field descriptions

Field Description

RXWATER Receive Watermark

When the number of datawords in the receive FIFO/buffer is equal to or greater than the value in this

register field, an interrupt via S1[RDRF] or a DMA request via C5[RDMAS] is generated as determined by

C5[RDMAS] and C2[RIE]. For proper operation, the value in RXWATER must be set to be less than the

receive FIFO/buffer size as indicated by PFIFO[RXFIFOSIZE] and PFIFO[RXFE] and must be greater

than 0.

47.3.22 UART FIFO Receive Count (UARTx_RCFIFO)

This is a read only register that indicates how many datawords are currently in the receive

FIFO/buffer. It may be read at any time.

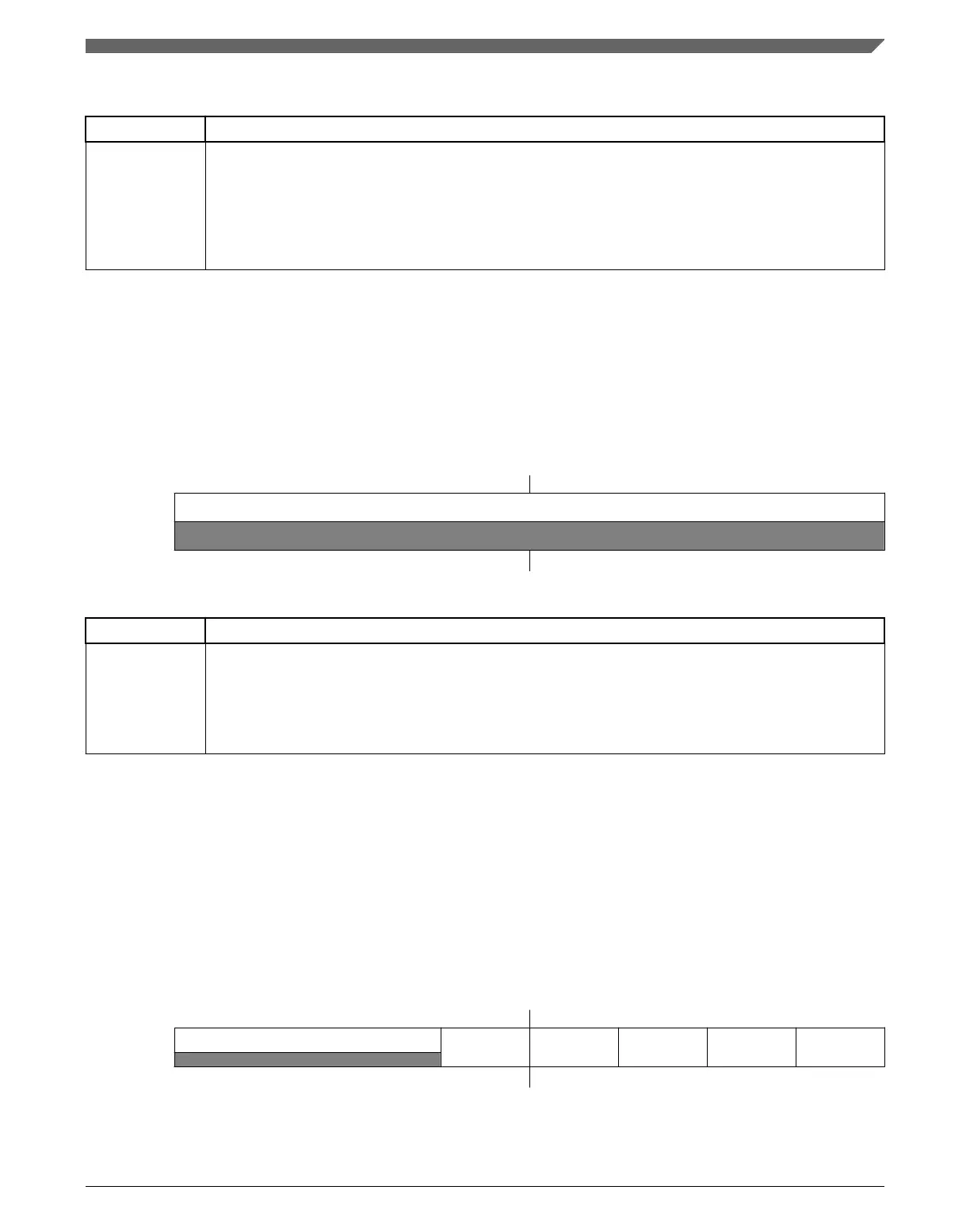

Address:

Base address + 16h offset

Bit 7 6 5 4 3 2 1 0

Read RXCOUNT

Write

Reset

0 0 0 0 0 0 0 0

UARTx_RCFIFO field descriptions

Field Description

RXCOUNT Receive Counter

The value in this register indicates the number of datawords that are in the receive FIFO/buffer. If a

dataword is being received, that is, in the receive shift register, it is not included in the count. This value

may be used in conjunction with PFIFO[RXFIFOSIZE] to calculate how much room is left in the receive

FIFO/buffer.

47.3.23 UART 7816 Control Register (UARTx_C7816)

The C7816 register is the primary control register for ISO-7816 specific functionality.

This register is specific to 7816 functionality and the values in this register have no effect

on UART operation and should be ignored if ISO_7816E is not set/enabled. This register

may be read at any time but values must be changed only when ISO_7816E is not set.

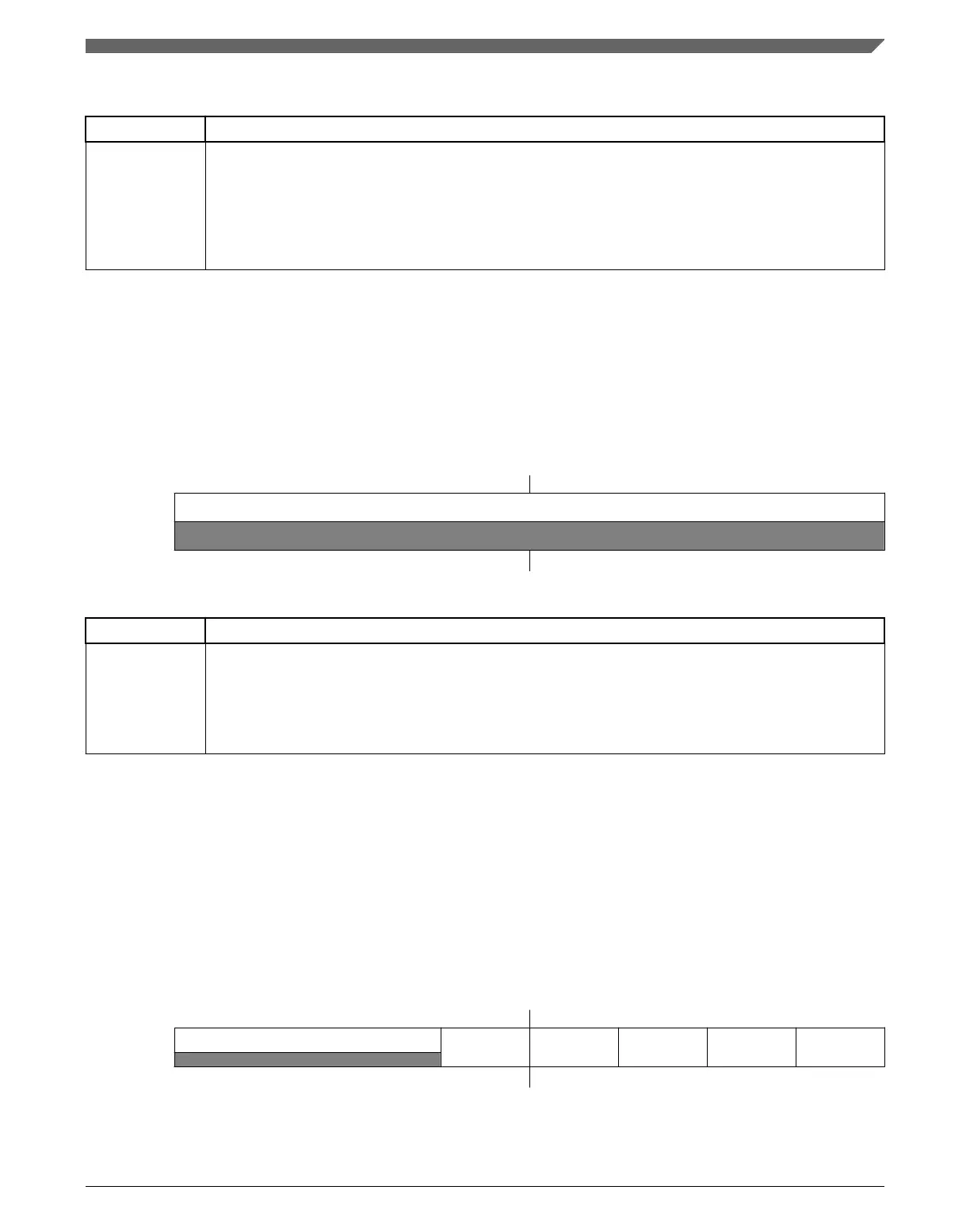

Address:

Base address + 18h offset

Bit 7 6 5 4 3 2 1 0

Read 0

ONACK ANACK INIT TTYPE ISO_7816E

Write

Reset

0 0 0 0 0 0 0 0

Chapter 47 Universal Asynchronous Receiver/Transmitter (UART)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1247

Loading...

Loading...