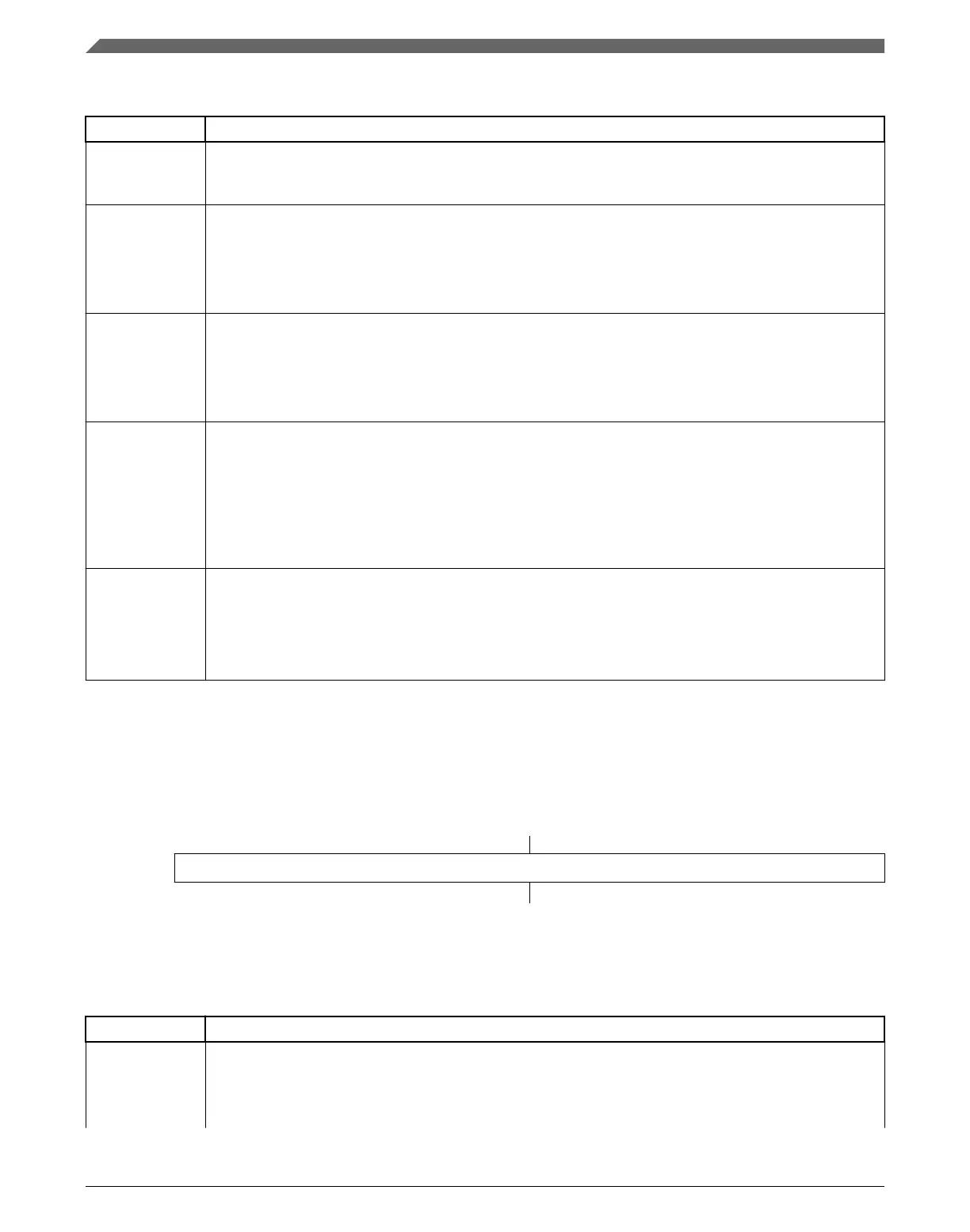

MCG_C2 field descriptions (continued)

Field Description

00 Encoding 0 — Low frequency range selected for the crystal oscillator .

01 Encoding 1 — High frequency range selected for the crystal oscillator .

1X Encoding 2 — Very high frequency range selected for the crystal oscillator .

3

HGO

High Gain Oscillator Select

Controls the crystal oscillator mode of operation. See the Oscillator (OSC) chapter for more details.

0 Configure crystal oscillator for low-power operation.

1 Configure crystal oscillator for high-gain operation.

2

EREFS

External Reference Select

Selects the source for the external reference clock. See the Oscillator (OSC) chapter for more details.

0 External reference clock requested.

1 Oscillator requested.

1

LP

Low Power Select

Controls whether the FLL or PLL is disabled in BLPI and BLPE modes. In FBE or PBE modes, setting this

bit to 1 will transition the MCG into BLPE mode; in FBI mode, setting this bit to 1 will transition the MCG

into BLPI mode. In any other MCG mode, LP bit has no affect.

0 FLL or PLL is not disabled in bypass modes.

1 FLL or PLL is disabled in bypass modes (lower power)

0

IRCS

Internal Reference Clock Select

Selects between the fast or slow internal reference clock source.

0 Slow internal reference clock selected.

1 Fast internal reference clock selected.

1. A value for FCFTRIM is loaded during reset from a factory programmed location.

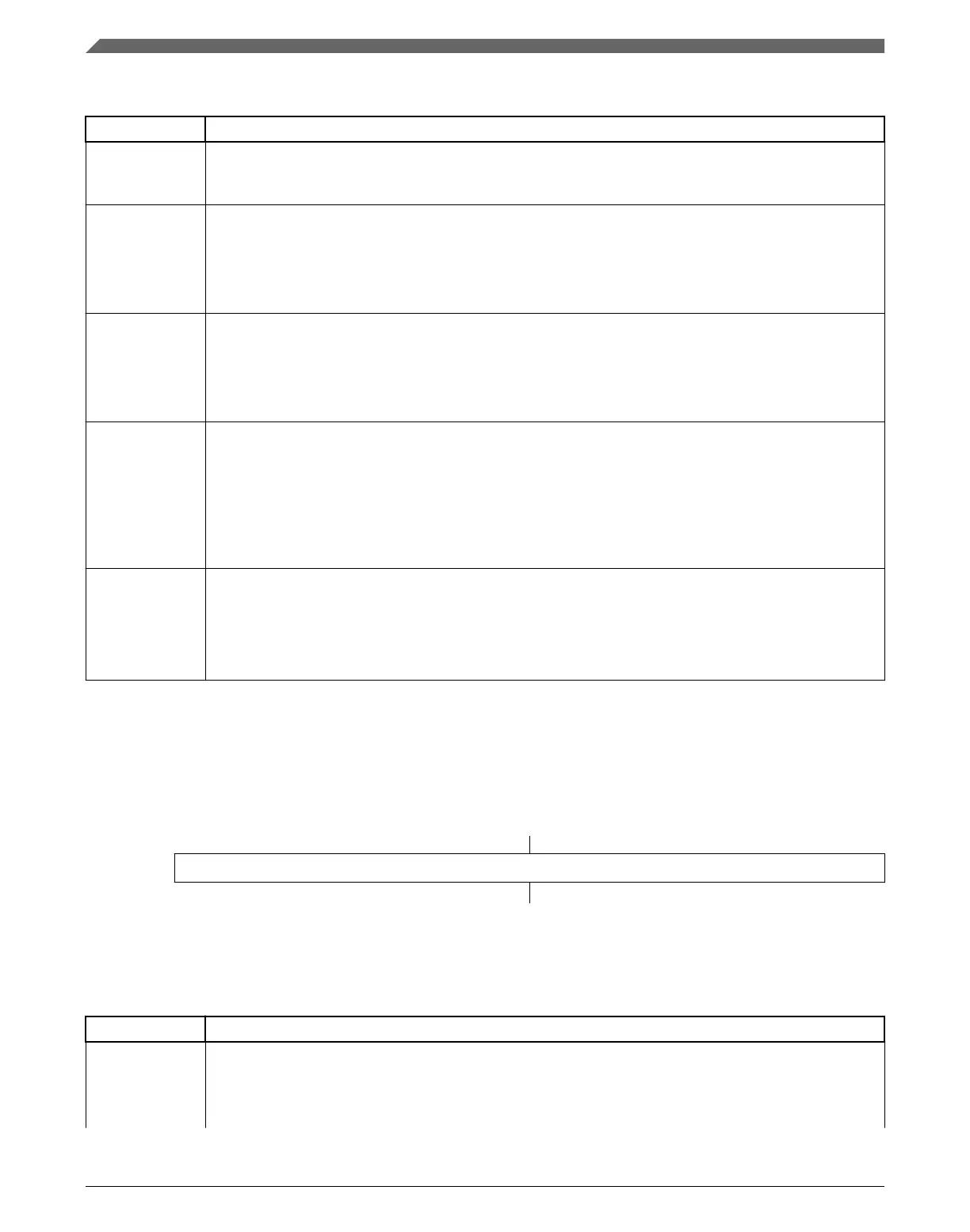

25.3.3 MCG Control 3 Register (MCG_C3)

Address: 4006_4000h base + 2h offset = 4006_4002h

Bit 7 6 5 4 3 2 1 0

Read

SCTRIM

Write

Reset

x* x* x* x* x* x* x* x*

* Notes:

x = Undefined at reset.•

MCG_C3 field descriptions

Field Description

SCTRIM Slow Internal Reference Clock Trim Setting

SCTRIM

1

controls the slow internal reference clock frequency by controlling the slow internal reference

clock period. The SCTRIM bits are binary weighted, that is, bit 1 adjusts twice as much as bit 0. Increasing

the binary value increases the period, and decreasing the value decreases the period.

Memory Map/Register Definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

546 NXP Semiconductors

Loading...

Loading...