46.4.6.6 Timeout interrupt in SMBus

When the IICIE bit is set, the I2C module asserts a timeout interrupt (outputs SLTF and

SHTF2) upon detection of any of the mentioned timeout conditions, with one exception.

The SCL high and SDA high TIMEOUT mechanism must not be used to influence the

timeout interrupt output, because this timeout indicates an idle condition on the bus.

SHTF1 rises when it matches the SCL high and SDA high TIMEOUT and falls

automatically just to indicate the bus status. The SHTF2's timeout period is the same as

that of SHTF1, which is short compared to that of SLTF, so another control bit,

SHTF2IE, is added to enable or disable it.

46.4.7

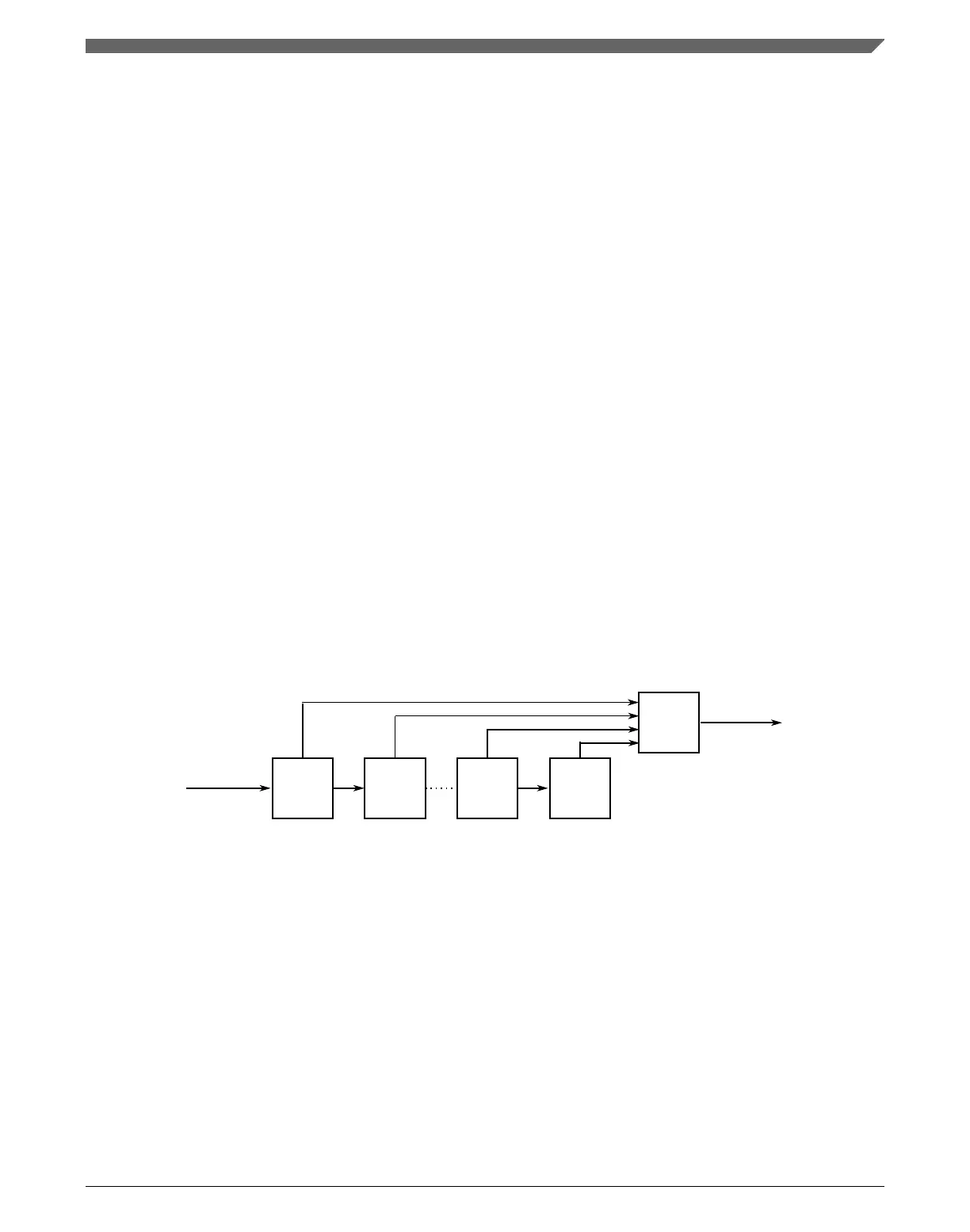

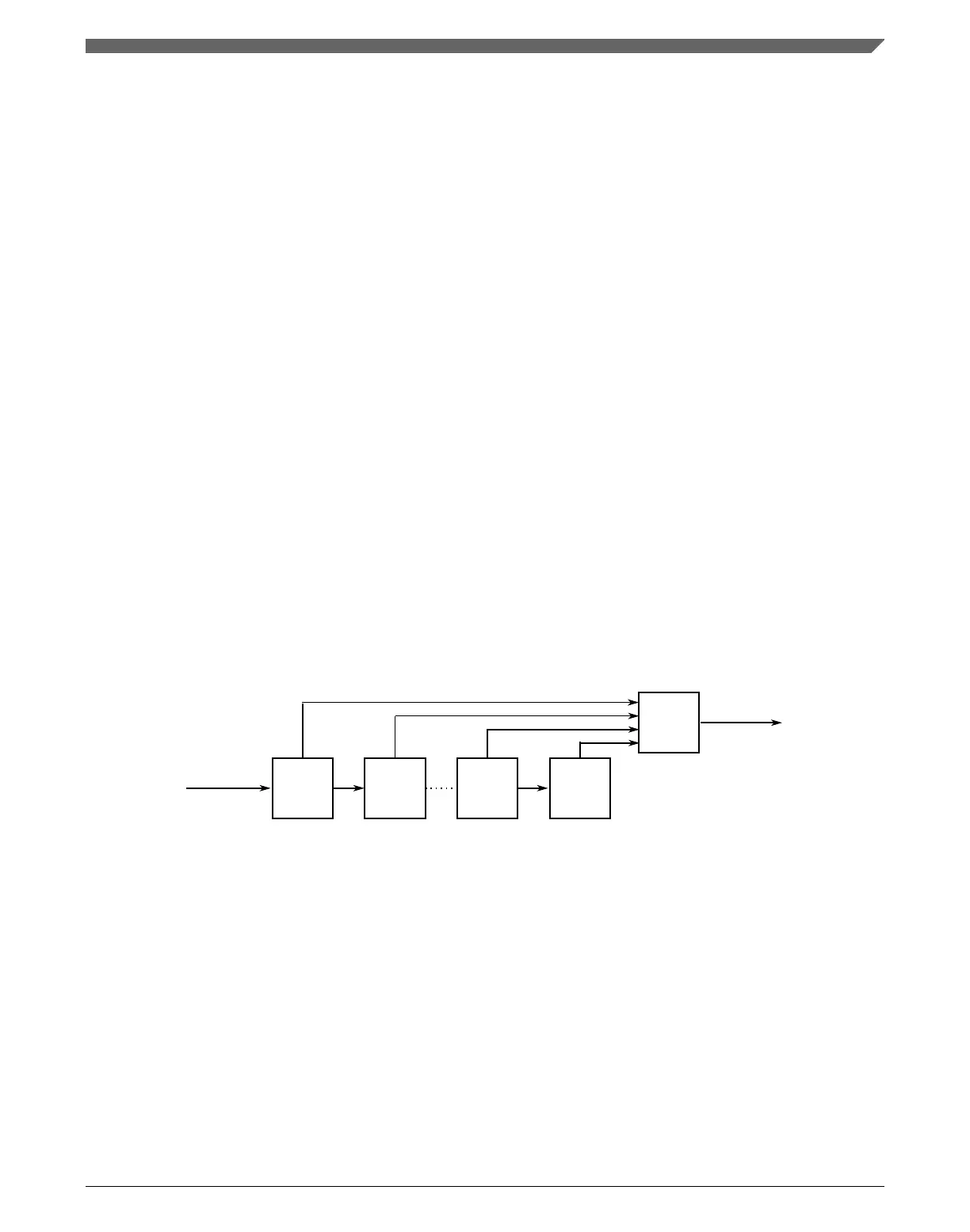

Programmable input glitch filter

An I2C glitch filter has been added outside legacy I2C modules but within the I2C

package. This filter can absorb glitches on the I2C clock and data lines for the I2C

module.

The width of the glitch to absorb can be specified in terms of the number of (half) I2C

module clock cycles. A single Programmable Input Glitch Filter control register is

provided. Effectively, any down-up-down or up-down-up transition on the data line that

occurs within the number of clock cycles programmed in this register is ignored by the

I2C module. The programmer must specify the size of the glitch (in terms of I2C module

clock cycles) for the filter to absorb and not pass.

SCL, SDA

external signals

DFF

Noise

suppress

circuits

SCL, SDA

internal signals

DFF DFF DFF

Figure 46-5. Programmable input glitch filter diagram

46.4.8

Address matching wake-up

When a primary, range, or general call address match occurs when the I2C module is in

slave receive mode, the MCU wakes from a low power mode where no peripheral bus is

running.

After the address matching IAAS bit is set, an interrupt is sent at the end of address

matching to wake the core.

Chapter 46 Inter-Integrated Circuit (I2C)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1209

Loading...

Loading...