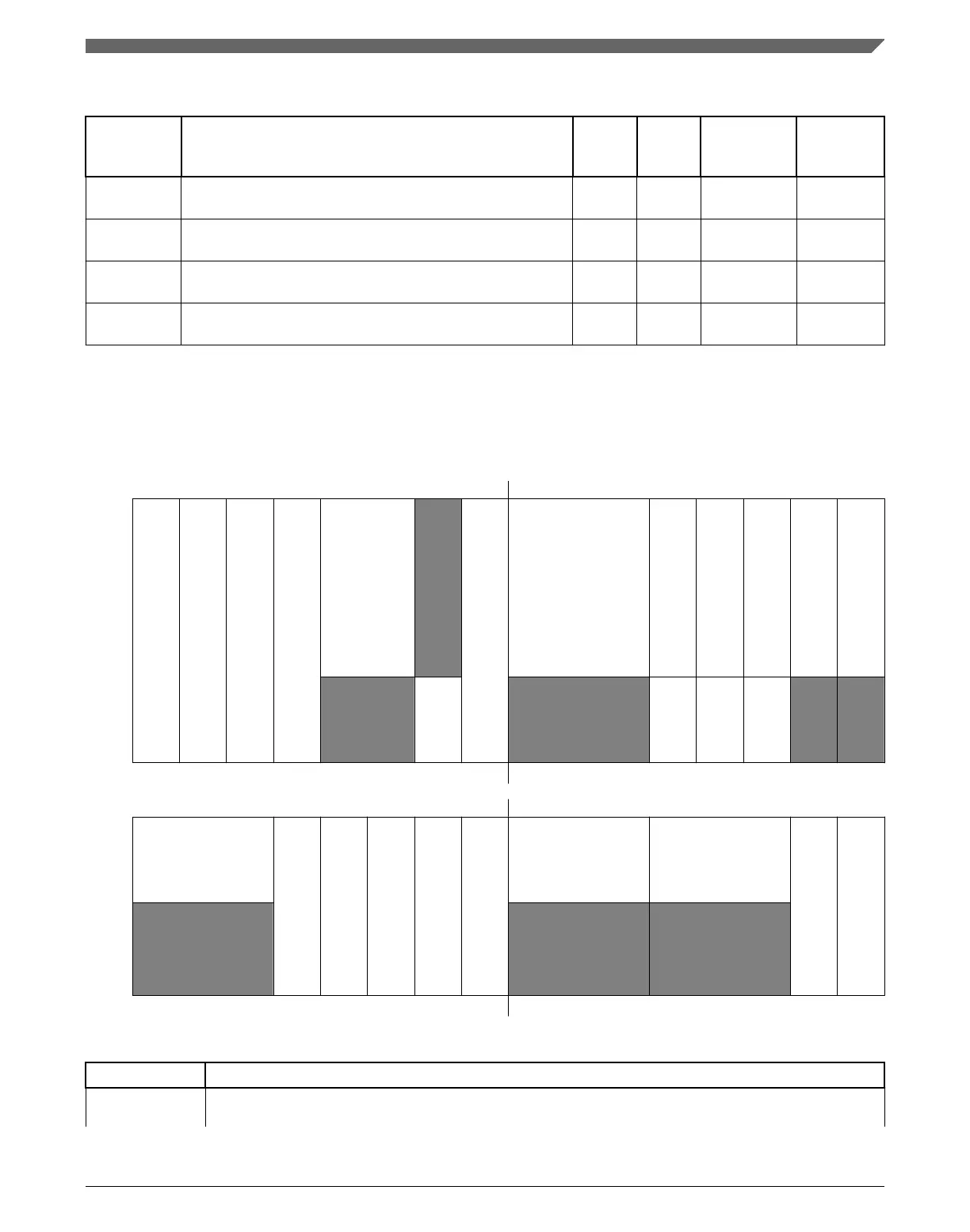

I2S memory map (continued)

Absolute

address

(hex)

Register name

Width

(in bits)

Access Reset value

Section/

page

4002_F0C0 SAI Receive FIFO Register (I2S0_RFR0) 32 R 0000_0000h

49.3.17/

1361

4002_F0E0 SAI Receive Mask Register (I2S0_RMR) 32 R/W 0000_0000h

49.3.18/

1361

4002_F100 SAI MCLK Control Register (I2S0_MCR) 32 R/W 0000_0000h

49.3.19/

1362

4002_F104 SAI MCLK Divide Register (I2S0_MDR) 32 R/W 0000_0000h

49.3.20/

1363

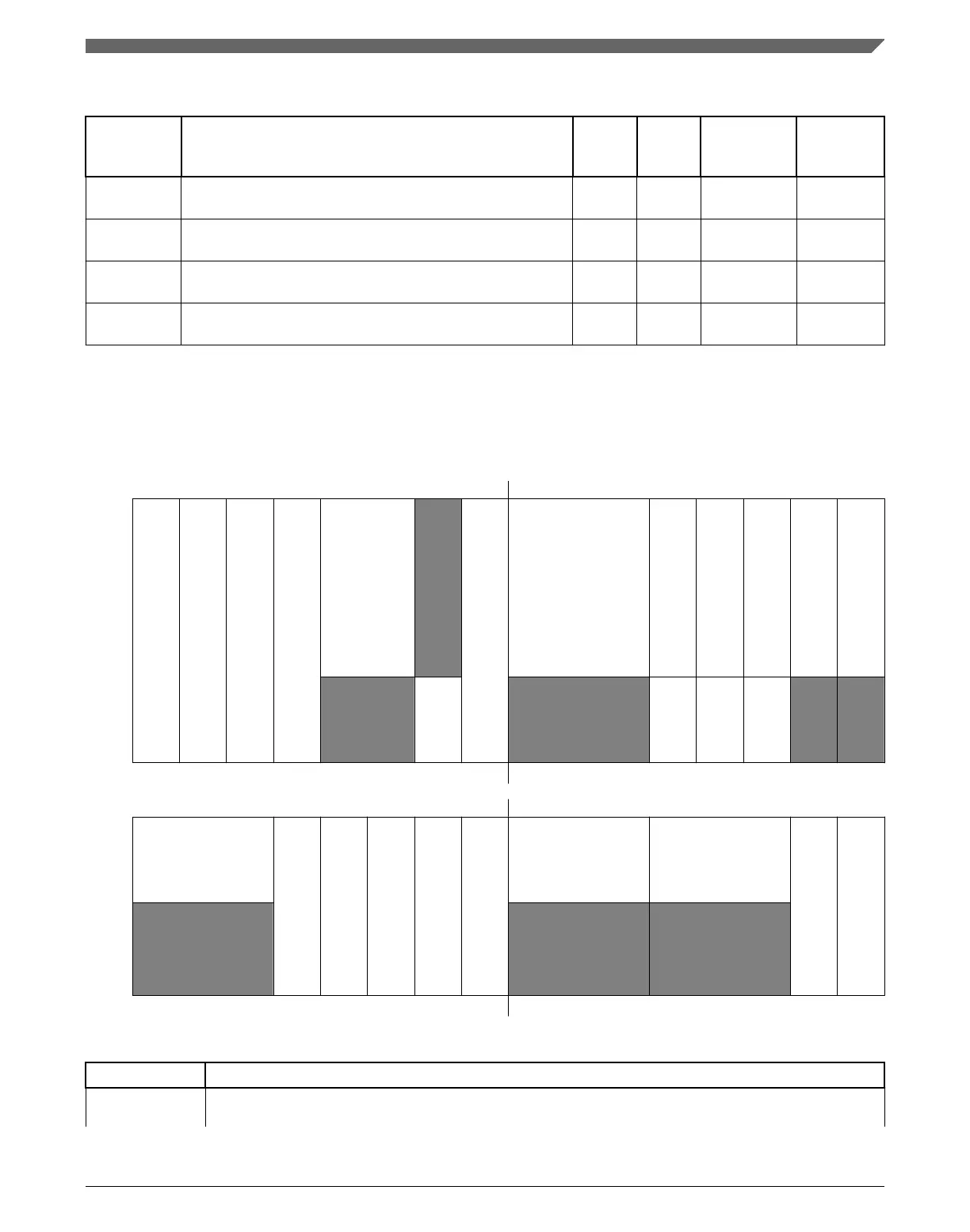

49.3.1 SAI Transmit Control Register (I2Sx_TCSR)

Address: 4002_F000h base + 0h offset = 4002_F000h

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

TE

STOPE

DBGE

BCE

0 0

SR

0

WSF

SEF FEF

FWF

FRF

W

FR w1c w1c w1c

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

WSIE SEIE FEIE FWIE FRIE

0 0

FWDE

FRDE

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

I2Sx_TCSR field descriptions

Field Description

31

TE

Transmitter Enable

Table continues on the next page...

Chapter 49 Integrated Interchip Sound (I2S) / Synchronous Audio Interface (SAI)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1341

Loading...

Loading...