UARTx_PFIFO field descriptions (continued)

Field Description

When this field is set, the built in FIFO structure for the receive buffer is enabled. The size of the FIFO

structure is indicated by the RXFIFOSIZE field. If this field is not set, the receive buffer operates as a FIFO

of depth one dataword regardless of the value in RXFIFOSIZE. Both C2[TE] and C2[RE] must be cleared

prior to changing this field. Additionally, TXFLUSH and RXFLUSH commands must be issued immediately

after changing this field.

0 Receive FIFO is not enabled. Buffer is depth 1. (Legacy support)

1 Receive FIFO is enabled. Buffer is depth indicted by RXFIFOSIZE.

RXFIFOSIZE Receive FIFO. Buffer Depth

The maximum number of receive datawords that can be stored in the receive buffer before an overrun

occurs. This field is read only.

000 Receive FIFO/Buffer depth = 1 dataword.

001 Receive FIFO/Buffer depth = 4 datawords.

010 Receive FIFO/Buffer depth = 8 datawords.

011 Receive FIFO/Buffer depth = 16 datawords.

100 Receive FIFO/Buffer depth = 32 datawords.

101 Receive FIFO/Buffer depth = 64 datawords.

110 Receive FIFO/Buffer depth = 128 datawords.

111 Reserved.

47.3.17 UART FIFO Control Register (UARTx_CFIFO)

This register provides the ability to program various control fields for FIFO operation.

This register may be read or written at any time. Note that writing to TXFLUSH and

RXFLUSH may result in data loss and requires careful action to prevent unintended/

unpredictable behavior. Therefore, it is recommended that TE and RE be cleared prior to

flushing the corresponding FIFO.

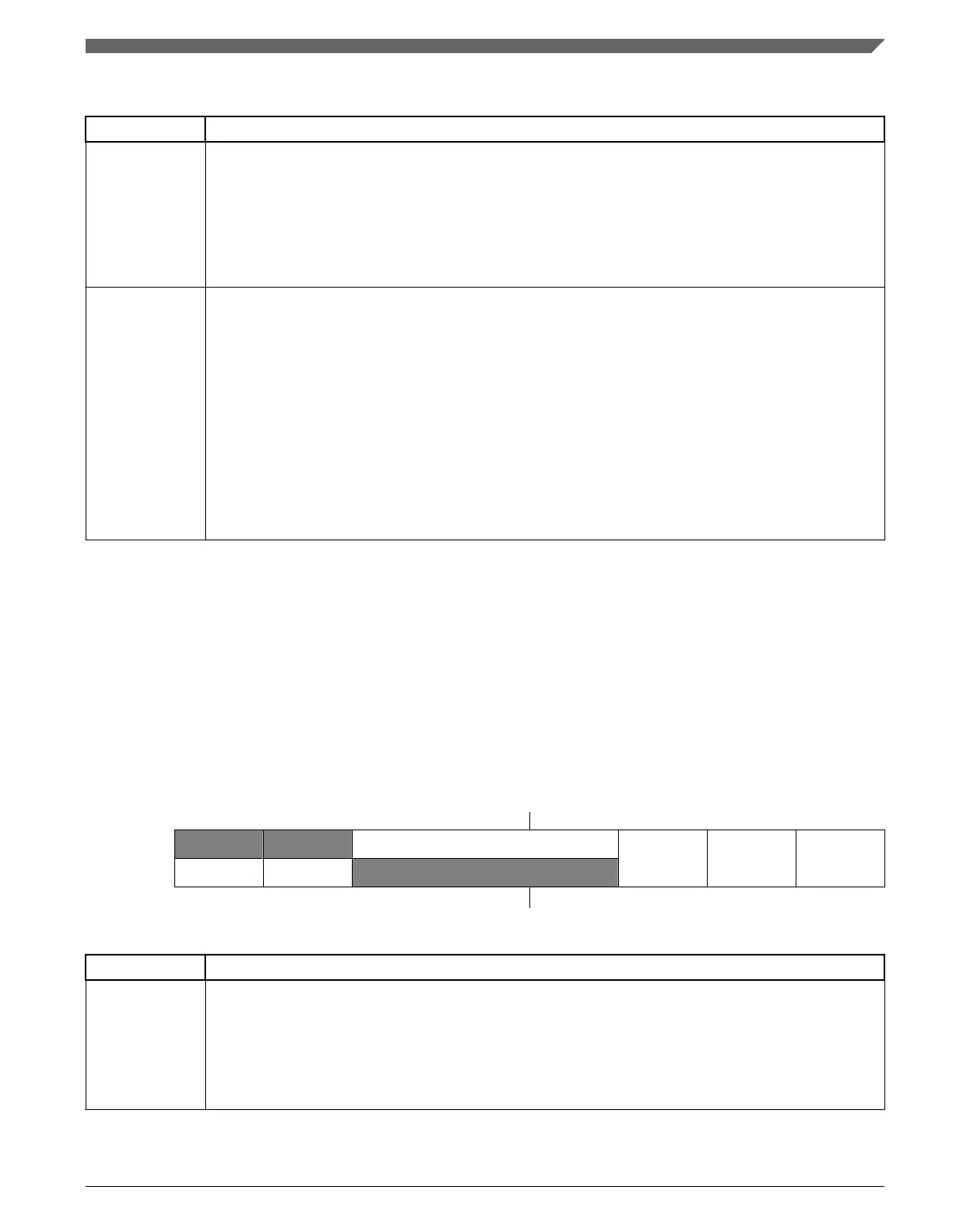

Address:

Base address + 11h offset

Bit 7 6 5 4 3 2 1 0

Read 0 0 0

RXOFE TXOFE RXUFE

Write TXFLUSH RXFLUSH

Reset

0 0 0 0 0 0 0 0

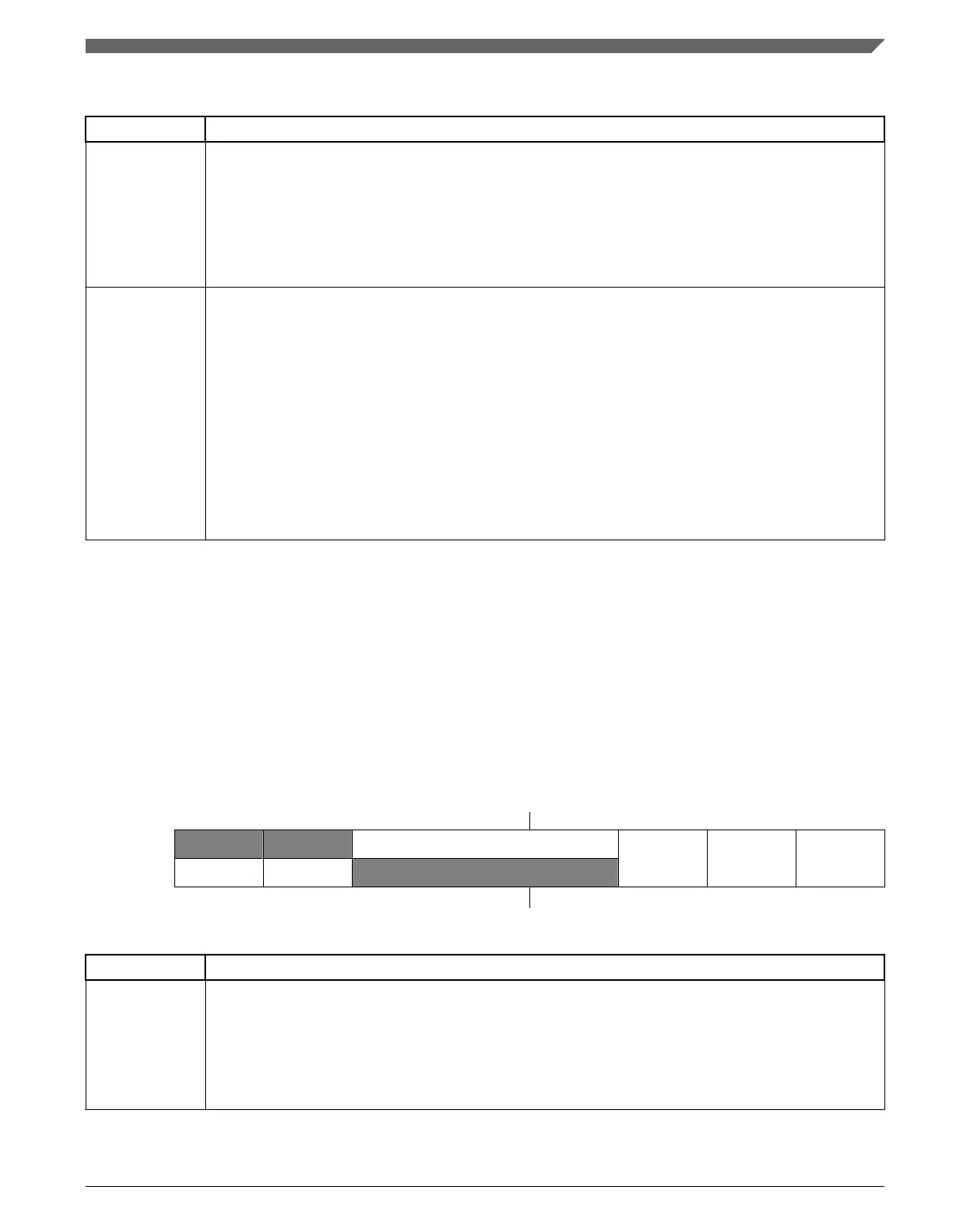

UARTx_CFIFO field descriptions

Field Description

7

TXFLUSH

Transmit FIFO/Buffer Flush

Writing to this field causes all data that is stored in the transmit FIFO/buffer to be flushed. This does not

affect data that is in the transmit shift register.

0 No flush operation occurs.

1 All data in the transmit FIFO/Buffer is cleared out.

Table continues on the next page...

Chapter 47 Universal Asynchronous Receiver/Transmitter (UART)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1243

Loading...

Loading...