39.3.6 Channel (n) Status And Control (FTMx_CnSC)

CnSC contains the channel-interrupt-status flag and control bits used to configure the

interrupt enable, channel configuration, and pin function.

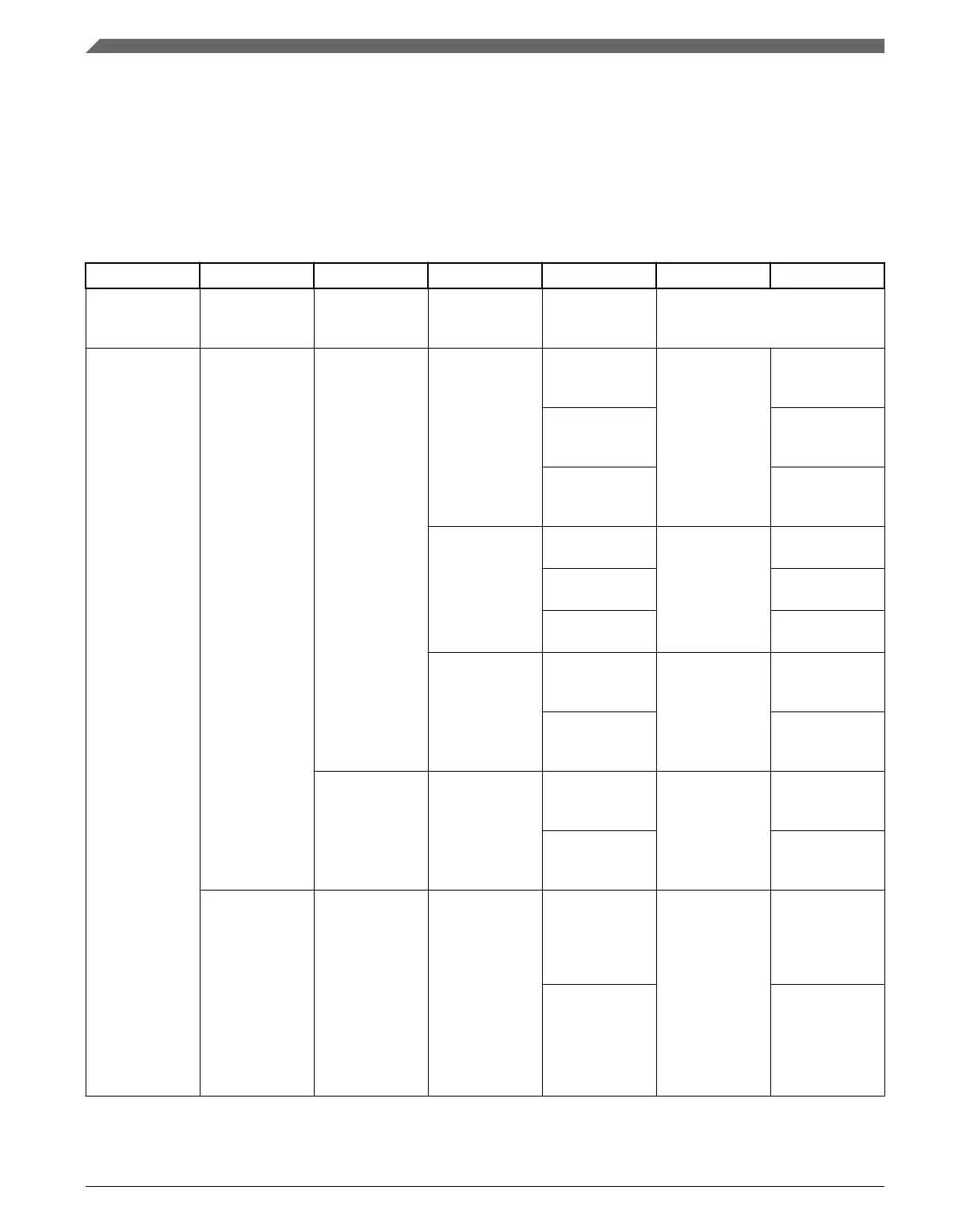

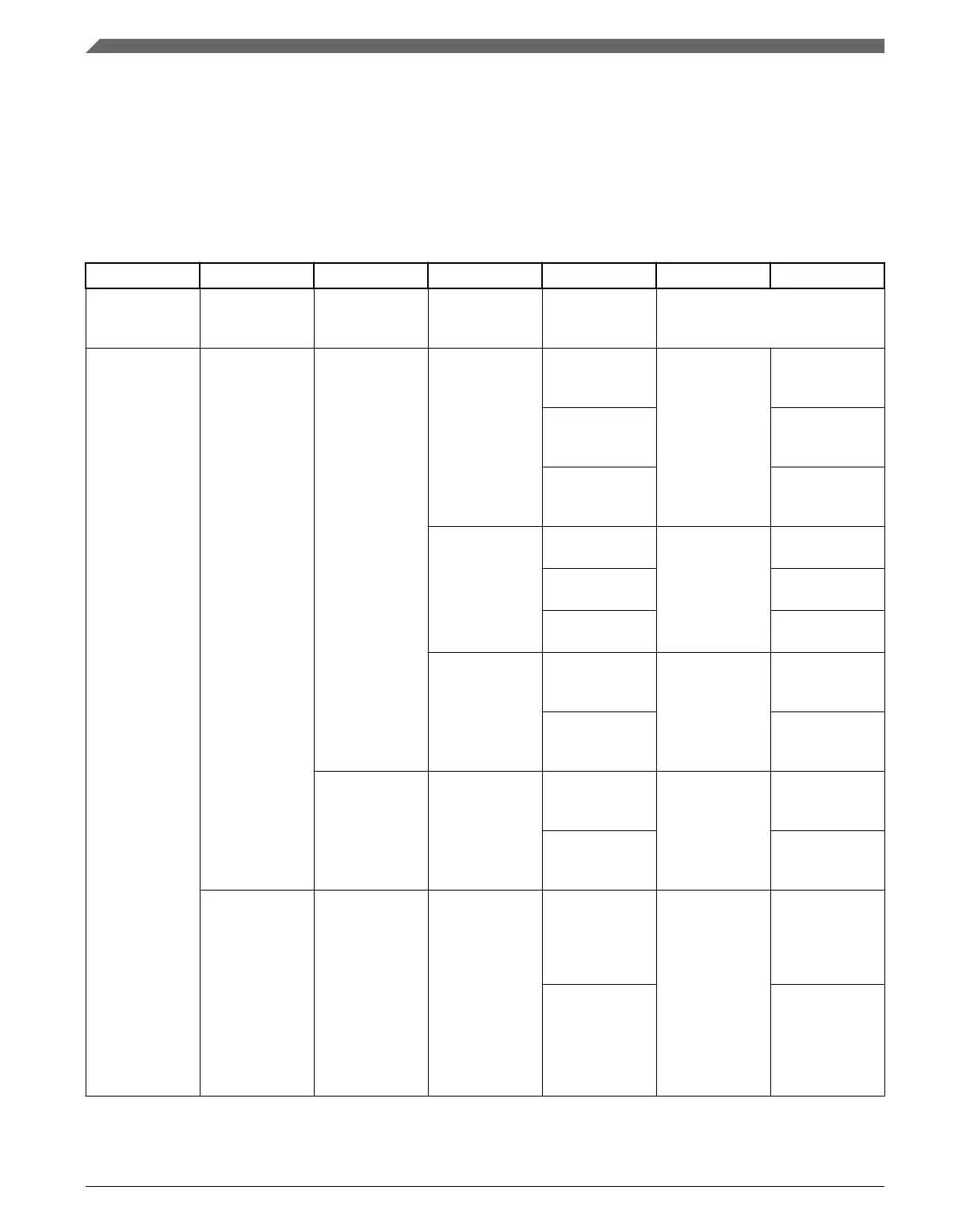

Table 39-2. Mode, edge, and level selection

DECAPEN COMBINE CPWMS MSnB:MSnA ELSnB:ELSnA Mode Configuration

X X X XX 00 Pin not used for FTM—revert the

channel pin to general purpose I/O

or other peripheral control

0 0 0 00 01 Input Capture Capture on

Rising Edge

Only

10 Capture on

Falling Edge

Only

11 Capture on

Rising or Falling

Edge

01 01 Output Compare Toggle Output

on match

10 Clear Output on

match

11 Set Output on

match

1X 10 Edge-Aligned

PWM

High-true pulses

(clear Output on

match)

X1 Low-true pulses

(set Output on

match)

1 XX 10 Center-Aligned

PWM

High-true pulses

(clear Output on

match-up)

X1 Low-true pulses

(set Output on

match-up)

1 0 XX 10 Combine PWM High-true pulses

(set on channel

(n) match, and

clear on channel

(n+1) match)

X1 Low-true pulses

(clear on

channel (n)

match, and set

on channel (n

+1) match)

Table continues on the next page...

Memory map and register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

906 NXP Semiconductors

Loading...

Loading...