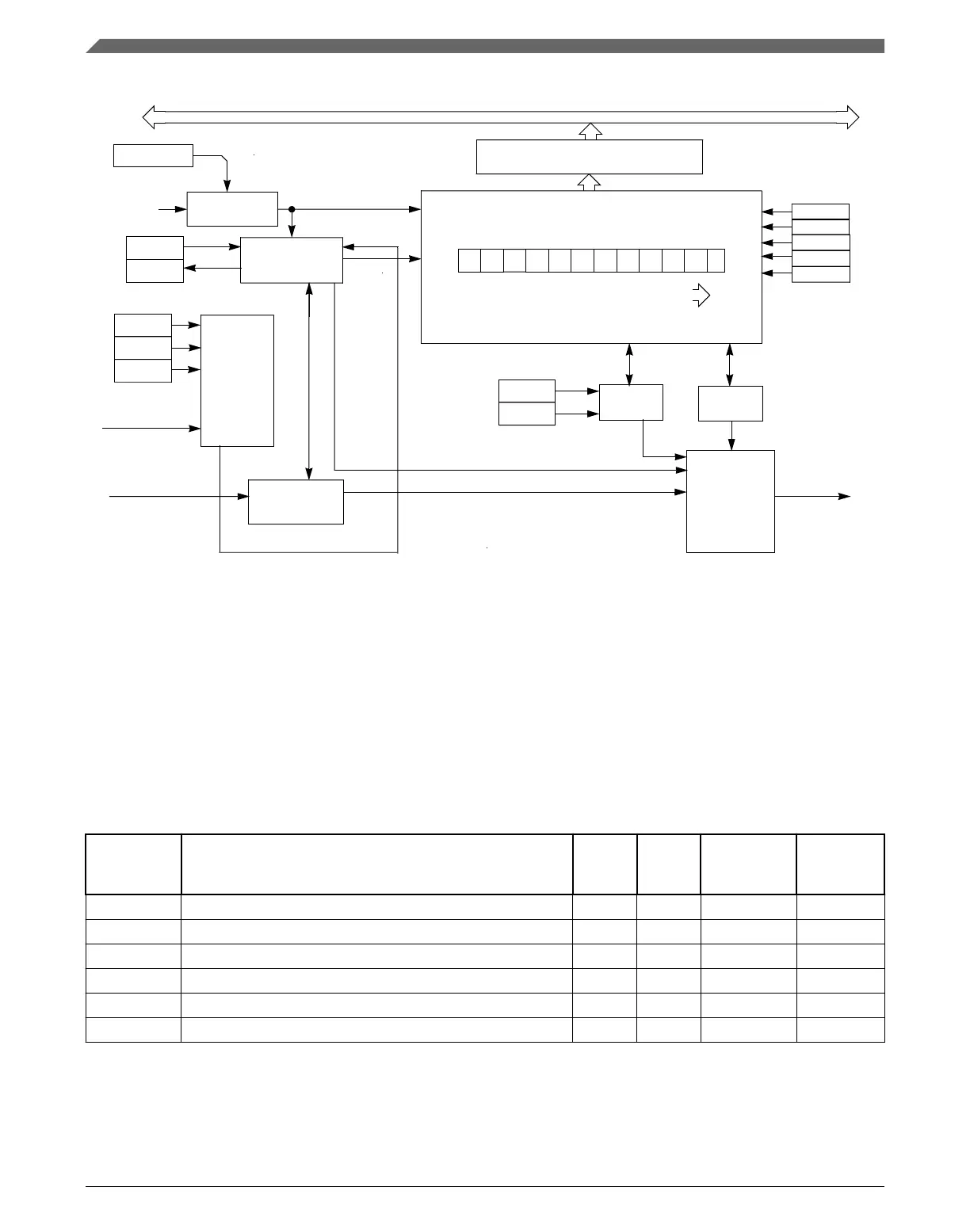

M

PE

PT

RE

VARIABLE 12-BIT RECEIVE

STOP

START

RECEIVE

WAKEUP

DATA BUFFER

INTERNAL BUS

SBR12:0

BAUDRATE

CLOCK

RAF

LOGIC

SHIFT DIRECTION

ACTIVE EDGE

DETECT

LBKDE

MSBF

GENERATOR

SHIFT REGISTER

M10

RXINV

IRQ / DMA

LOGIC

DMA Requests

IRQ Requests

PARITY

LOGIC

CONTROL

RxD

RxD

LOOPS

RSRC

From Transmitter

RECEIVER

SOURCE

CONTROL

MODULE

ASYNCH

Figure 48-2. LPUART receiver block diagram

48.2

Register definition

The LPUART includes registers to control baud rate, select LPUART options, report

LPUART status, and for transmit/receive data. Access to an address outside the valid

memory map will generate a bus error.

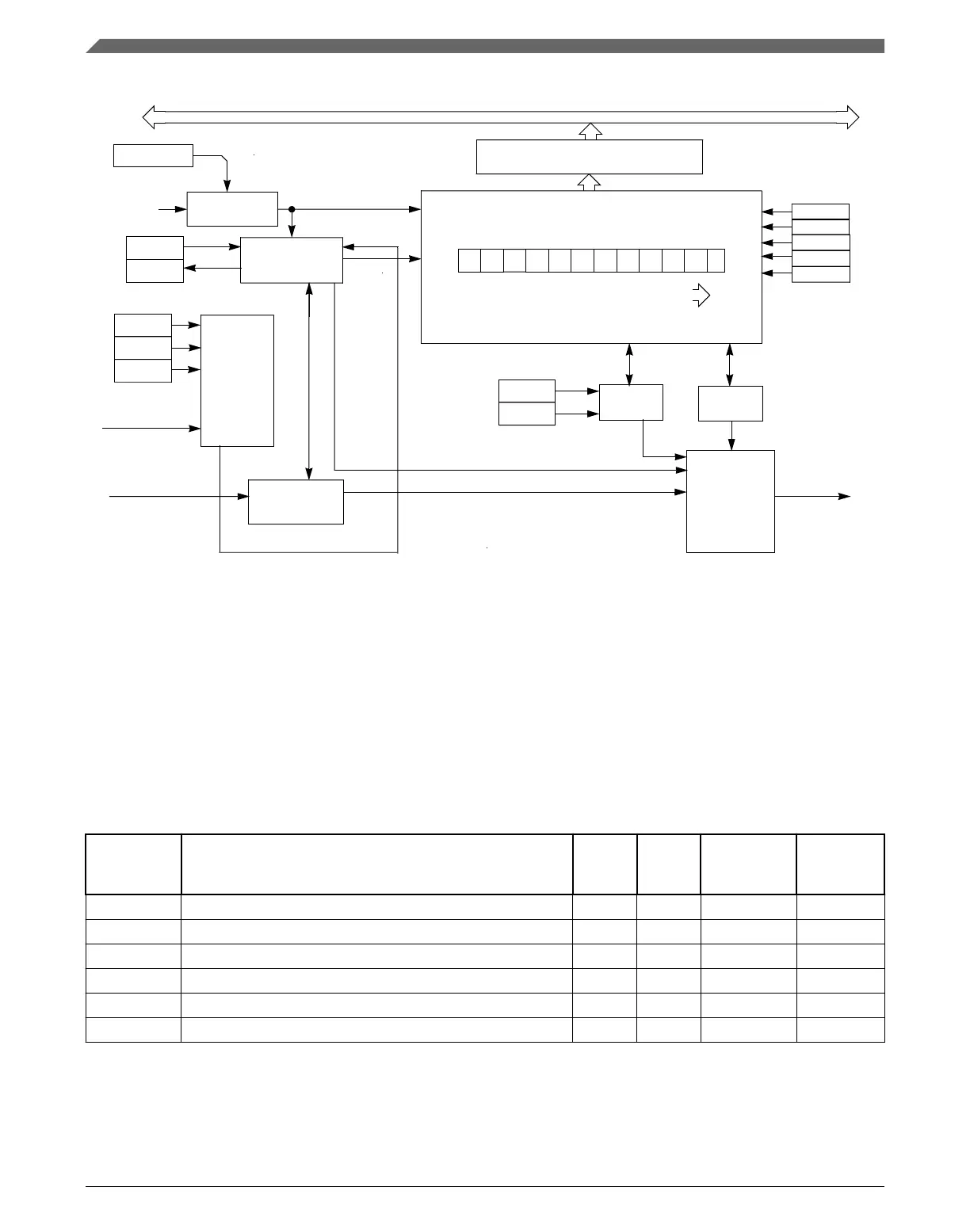

LPUART memory map

Absolute

address

(hex)

Register name

Width

(in bits)

Access Reset value

Section/

page

4002_A000 LPUART Baud Rate Register (LPUART0_BAUD) 32 R/W 0F00_0004h 48.2.1/1307

4002_A004 LPUART Status Register (LPUART0_STAT) 32 R/W 00C0_0000h 48.2.2/1309

4002_A008 LPUART Control Register (LPUART0_CTRL) 32 R/W 0000_0000h 48.2.3/1313

4002_A00C LPUART Data Register (LPUART0_DATA) 32 R/W 0000_1000h 48.2.4/1318

4002_A010 LPUART Match Address Register (LPUART0_MATCH) 32 R/W 0000_0000h 48.2.5/1320

4002_A014 LPUART Modem IrDA Register (LPUART0_MODIR) 32 R/W 0000_0000h 48.2.6/1320

Register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1306 NXP Semiconductors

Loading...

Loading...