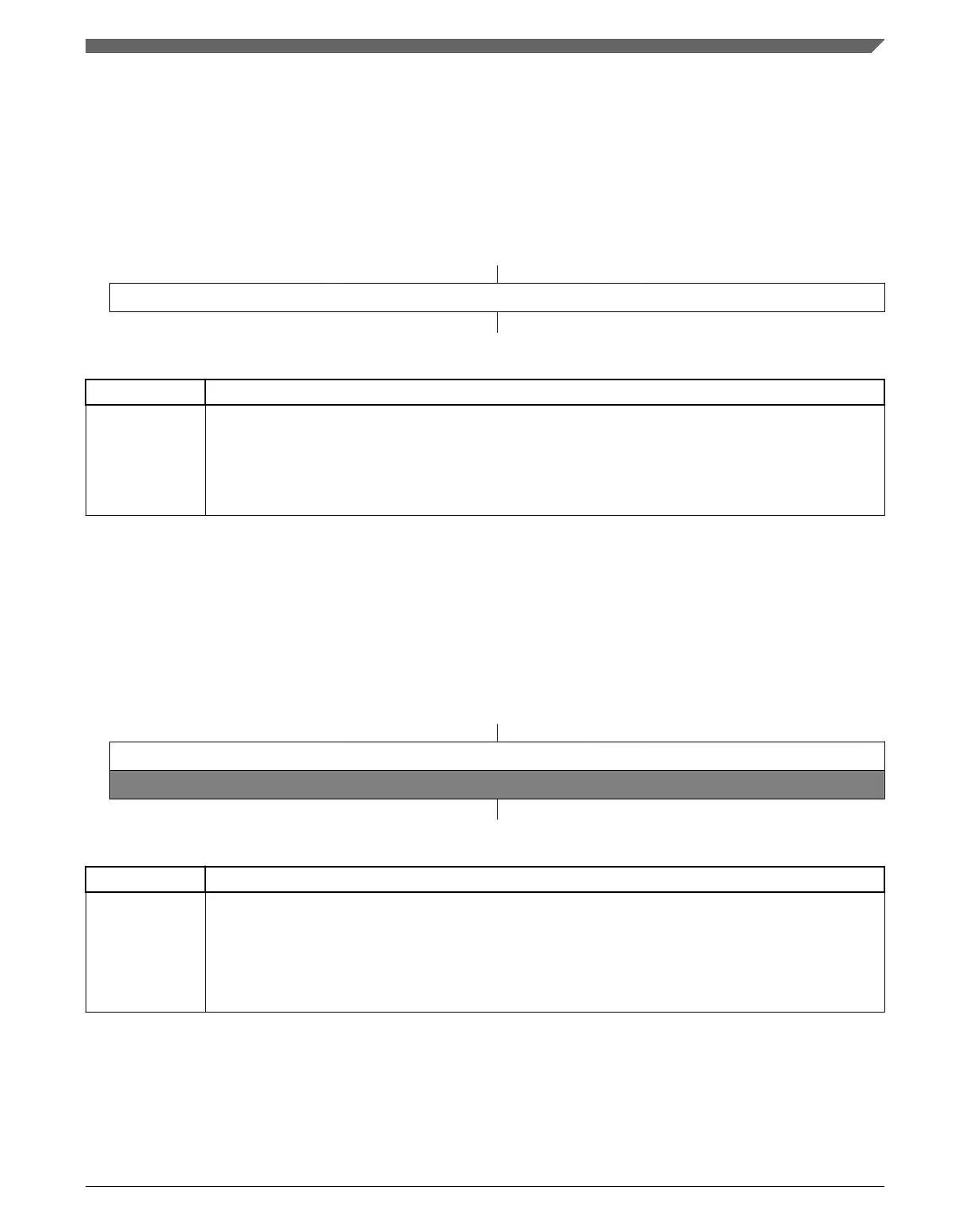

40.3.2 Timer Load Value Register (PIT_LDVALn)

These registers select the timeout period for the timer interrupts.

Access: User read/write

Address: 4003_7000h base + 100h offset + (16d × i), where i=0d to 3d

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

TSV

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

PIT_LDVALn field descriptions

Field Description

TSV Timer Start Value

Sets the timer start value. The timer will count down until it reaches 0, then it will generate an interrupt and

load this register value again. Writing a new value to this register will not restart the timer; instead the

value will be loaded after the timer expires. To abort the current cycle and start a timer period with the new

value, the timer must be disabled and enabled again.

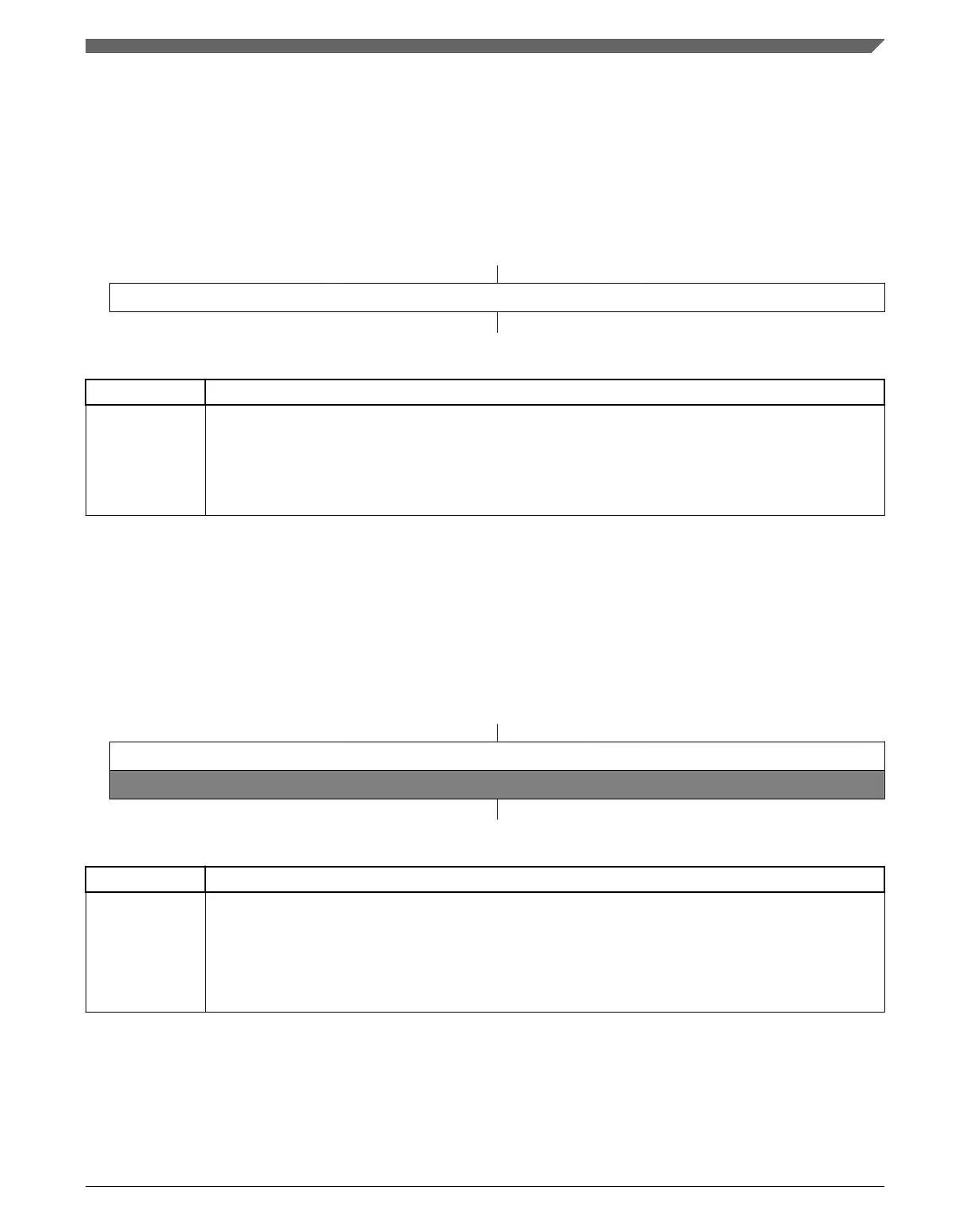

40.3.3 Current Timer Value Register (PIT_CVALn)

These registers indicate the current timer position.

Access: User read only

Address:

4003_7000h base + 104h offset + (16d × i), where i=0d to 3d

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

TVL

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

PIT_CVALn field descriptions

Field Description

TVL Current Timer Value

Represents the current timer value, if the timer is enabled.

NOTE:

• If the timer is disabled, do not use this field as its value is unreliable.

• The timer uses a downcounter. The timer values are frozen in Debug mode if MCR[FRZ] is

set.

Chapter 40 Periodic Interrupt Timer (PIT)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1033

Loading...

Loading...