I2Sx_RDRn field descriptions

Field Description

RDR Receive Data Register

The corresponding RCR3[RCE] bit must be set before accessing the channel's receive data register.

Reads from this register when the receive FIFO is not empty will return the data from the top of the receive

FIFO. Reads from this register when the receive FIFO is empty are ignored.

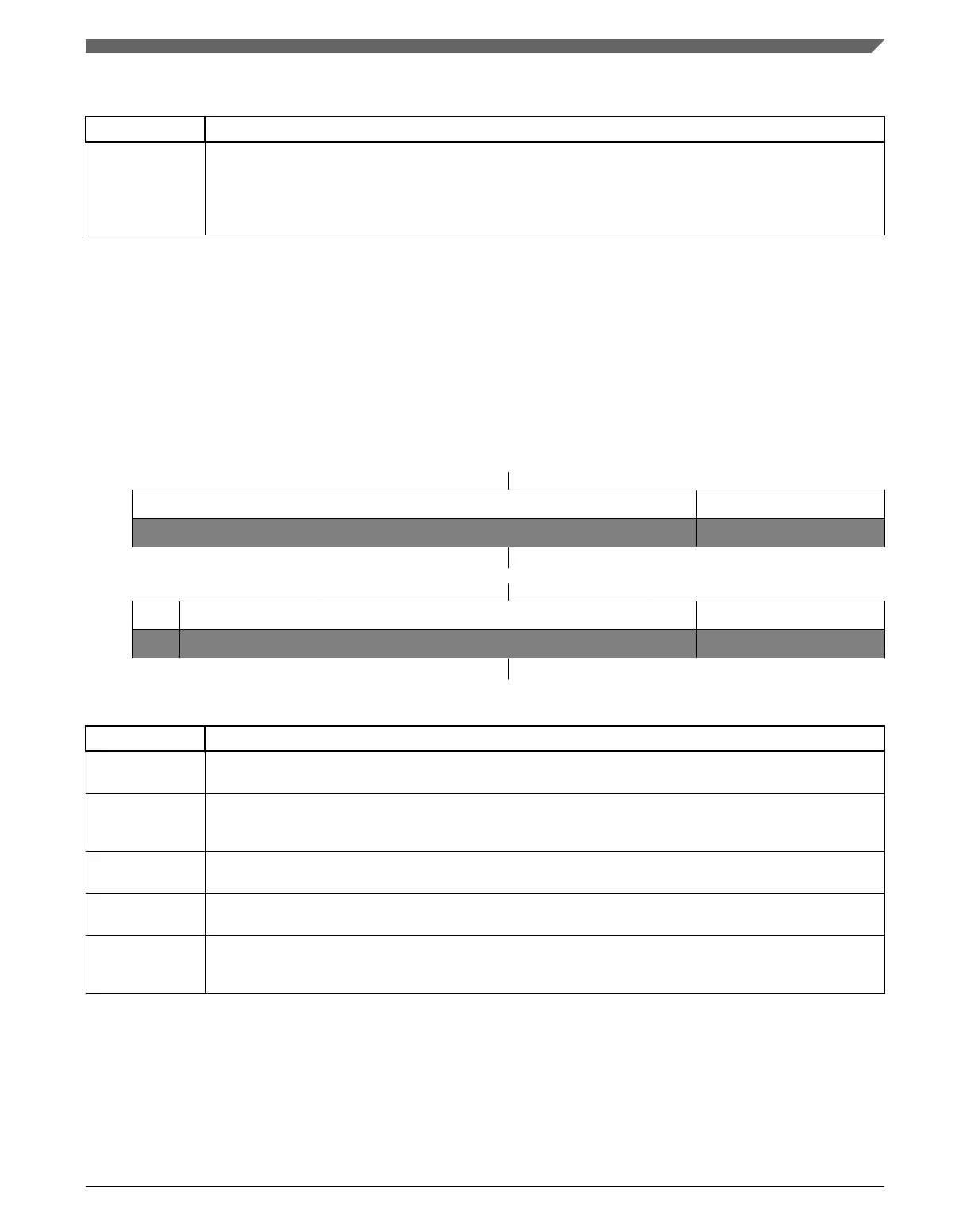

49.3.17 SAI Receive FIFO Register (I2Sx_RFRn)

The MSB of the read and write pointers is used to distinguish between FIFO full and

empty conditions. If the read and write pointers are identical, then the FIFO is empty. If

the read and write pointers are identical except for the MSB, then the FIFO is full.

Address:

4002_F000h base + C0h offset + (4d × i), where i=0d to 0d

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

0 WFP

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

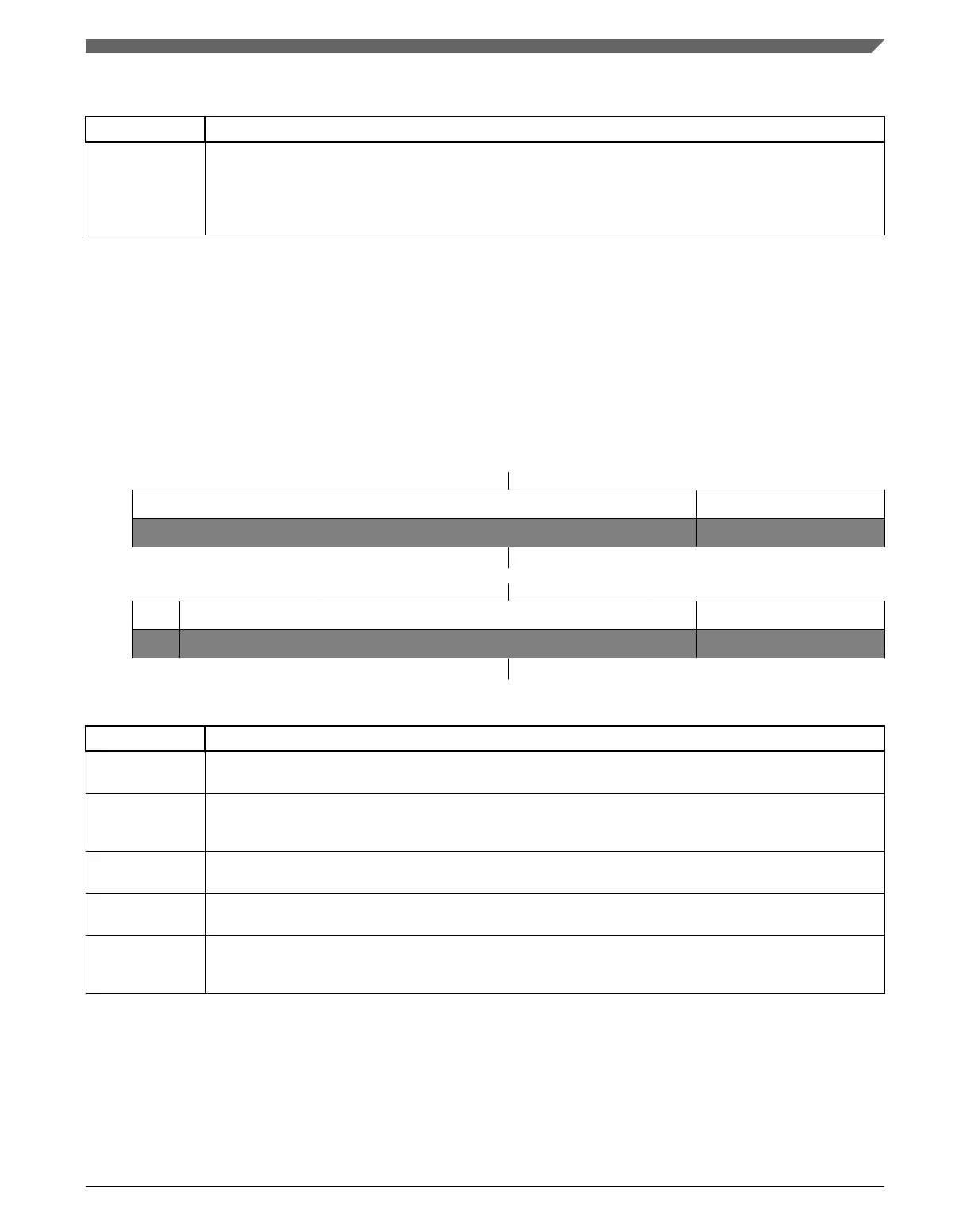

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0 0 RFP

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

I2Sx_RFRn field descriptions

Field Description

31–20

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

19–16

WFP

Write FIFO Pointer

FIFO write pointer for receive data channel.

15

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

14–4

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

RFP Read FIFO Pointer

FIFO read pointer for receive data channel.

49.3.18 SAI Receive Mask Register (I2Sx_RMR)

This register is double-buffered and updates:

Chapter 49 Integrated Interchip Sound (I2S) / Synchronous Audio Interface (SAI)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1361

Loading...

Loading...