WDOG_STCTRLH field descriptions (continued)

Field Description

0

WDOGEN

Enables or disables the WDOG’s operation. In the disabled state, the watchdog timer is kept in the reset

state, but the other exception conditions can still trigger a reset/interrupt. A change in the value of this bit

must be held for more than one WDOG_CLK cycle for the WDOG to be enabled or disabled.

0 WDOG is disabled.

1 WDOG is enabled.

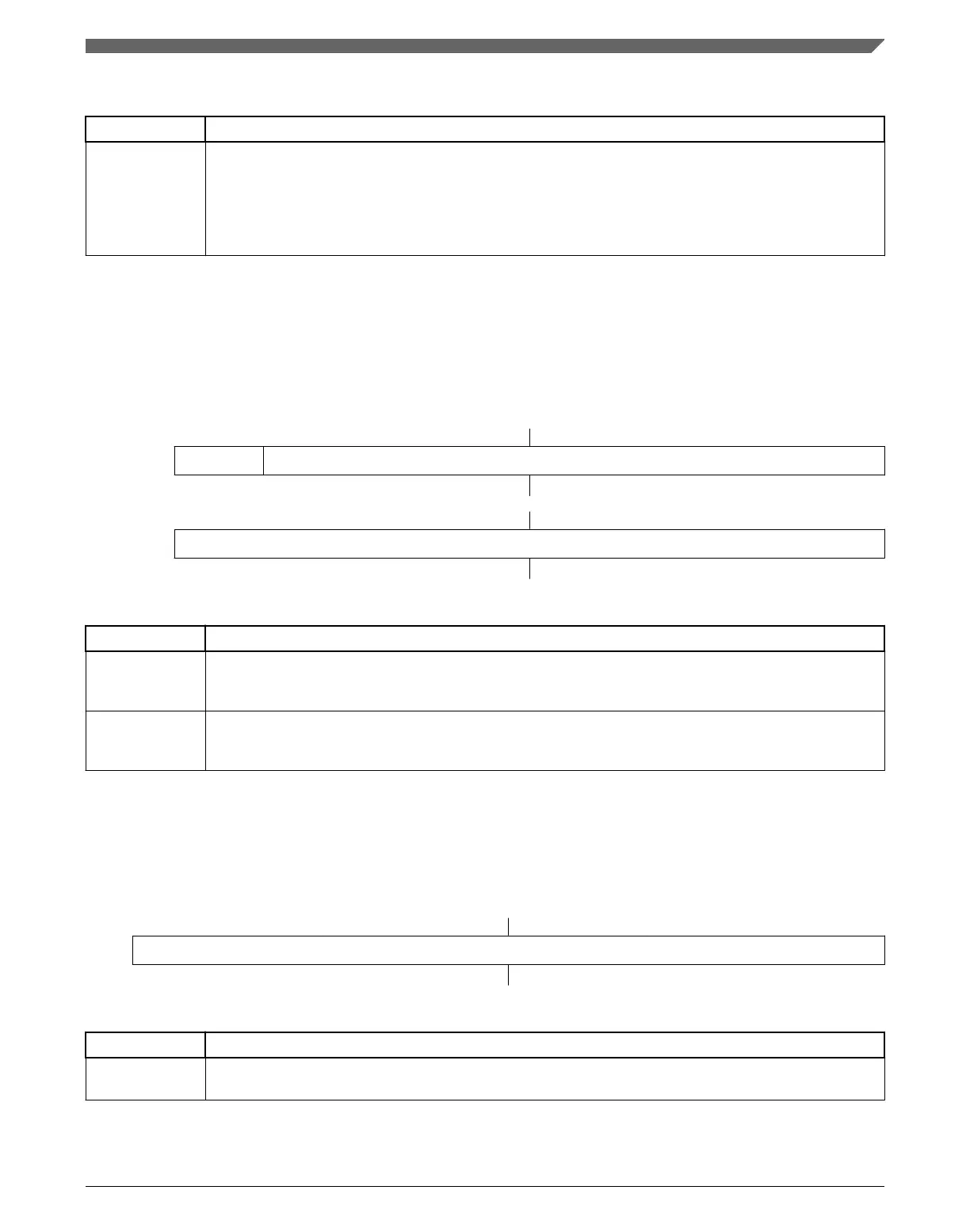

24.7.2 Watchdog Status and Control Register Low

(WDOG_STCTRLL)

Address: 4005_2000h base + 2h offset = 4005_2002h

Bit 15 14 13 12 11 10 9 8

Read

INTFLG Reserved

Write

Reset

0 0 0 0 0 0 0 0

Bit

7 6 5 4 3 2 1 0

Read

Reserved

Write

Reset

0 0 0 0 0 0 0 1

WDOG_STCTRLL field descriptions

Field Description

15

INTFLG

Interrupt flag. It is set when an exception occurs. IRQRSTEN = 1 is a precondition to set this flag. INTFLG

= 1 results in an interrupt being issued followed by a reset, WCT later. The interrupt can be cleared by

writing 1 to this bit. It also gets cleared on a system reset.

Reserved This field is reserved.

NOTE:

Do not modify this field value.

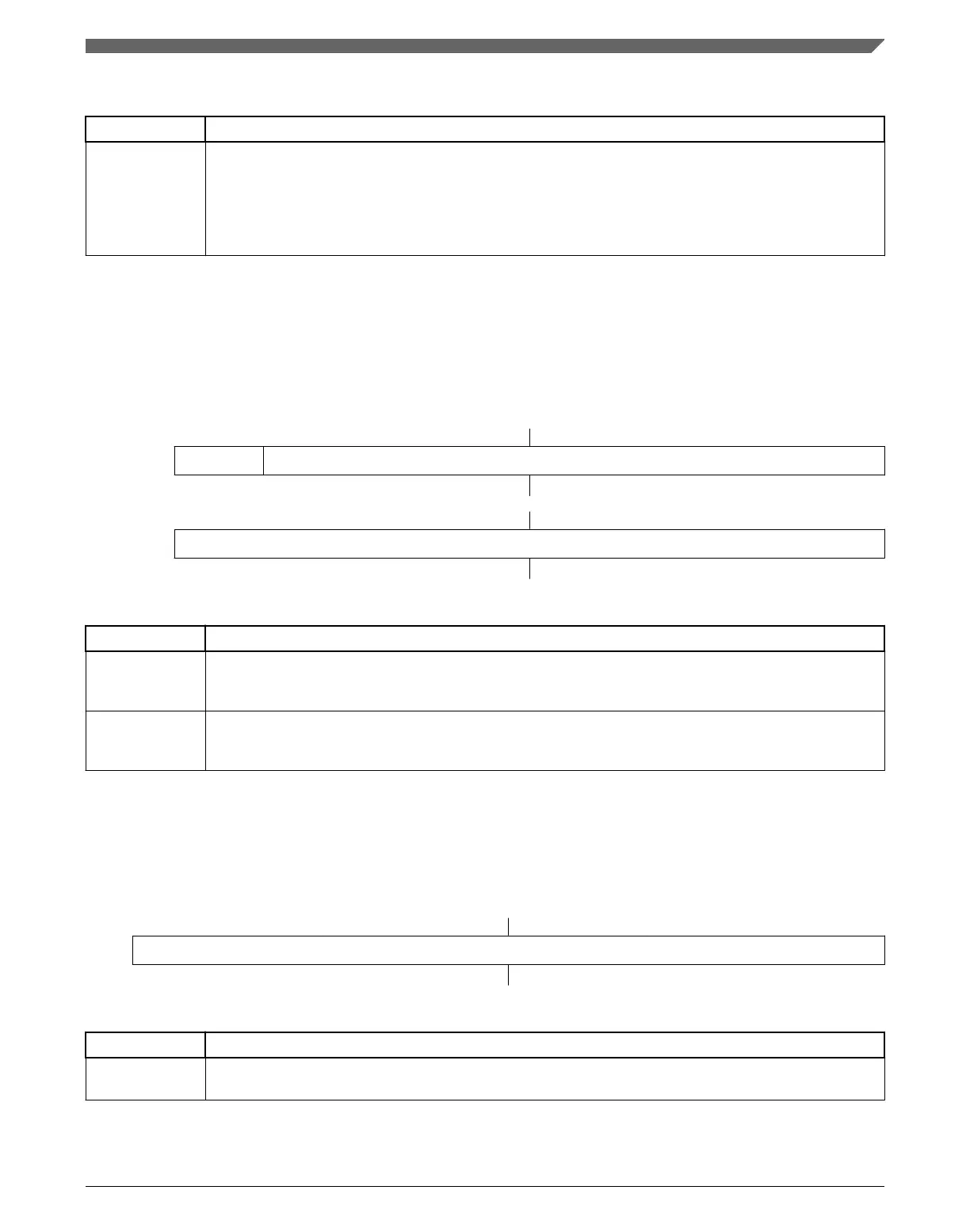

24.7.3 Watchdog Time-out Value Register High (WDOG_TOVALH)

Address: 4005_2000h base + 4h offset = 4005_2004h

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Read

TOVALHIGH

Write

Reset

0 0 0 0 0 0 0 0 0 1 0 0 1 1 0 0

WDOG_TOVALH field descriptions

Field Description

TOVALHIGH Defines the upper 16 bits of the 32-bit time-out value for the watchdog timer. It is defined in terms of cycles

of the watchdog clock.

Chapter 24 Watchdog Timer (WDOG)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 531

Loading...

Loading...