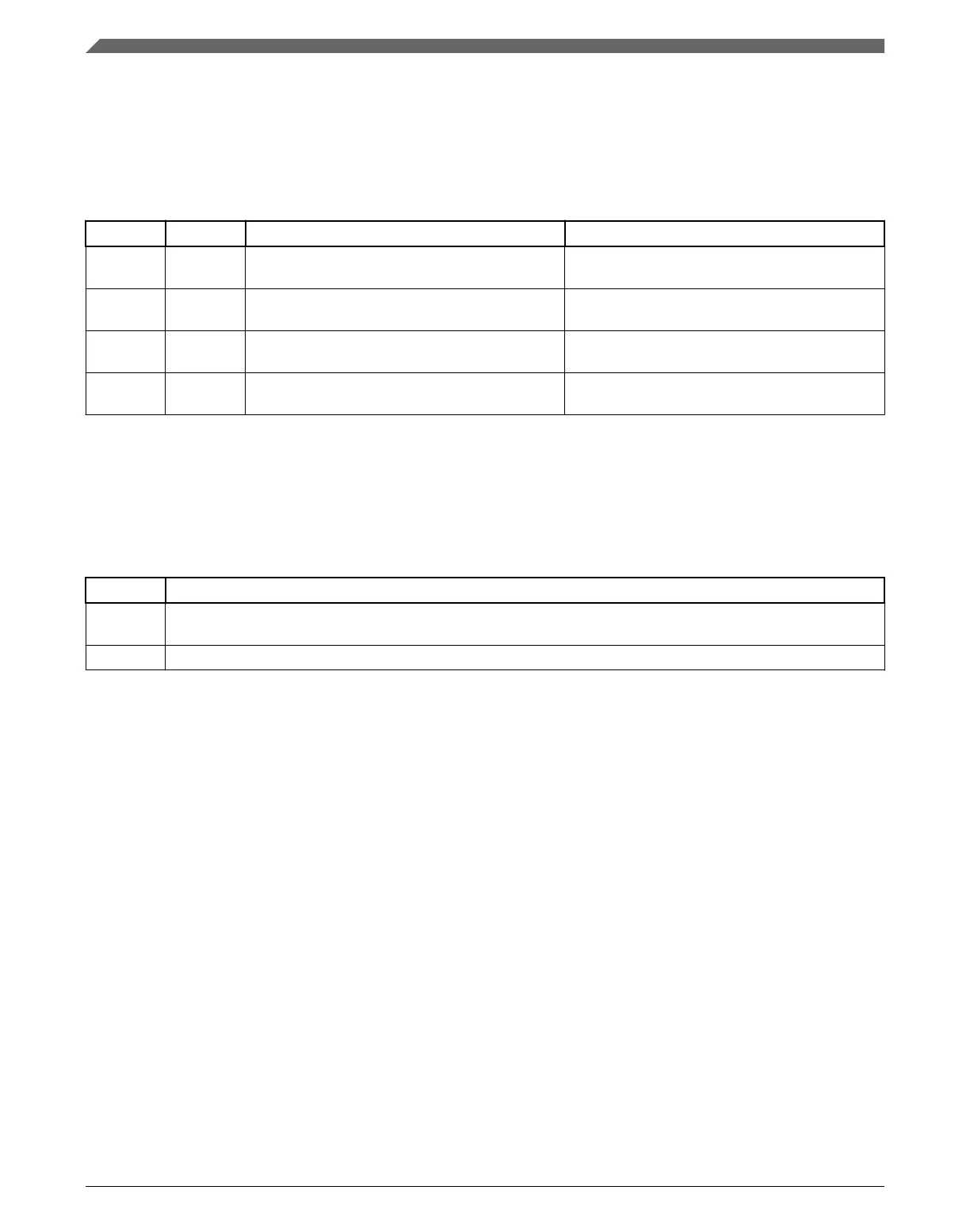

39.4.23 DMA

The channel generates a DMA transfer request according to DMA and CHnIE bits. See

the following table.

Table 39-13. Channel DMA transfer request

DMA CHnIE Channel DMA Transfer Request Channel Interrupt

0 0 The channel DMA transfer request is not

generated.

The channel interrupt is not generated.

0 1 The channel DMA transfer request is not

generated.

The channel interrupt is generated if (CHnF = 1).

1 0 The channel DMA transfer request is not

generated.

The channel interrupt is not generated.

1 1 The channel DMA transfer request is generated if

(CHnF = 1).

The channel interrupt is not generated.

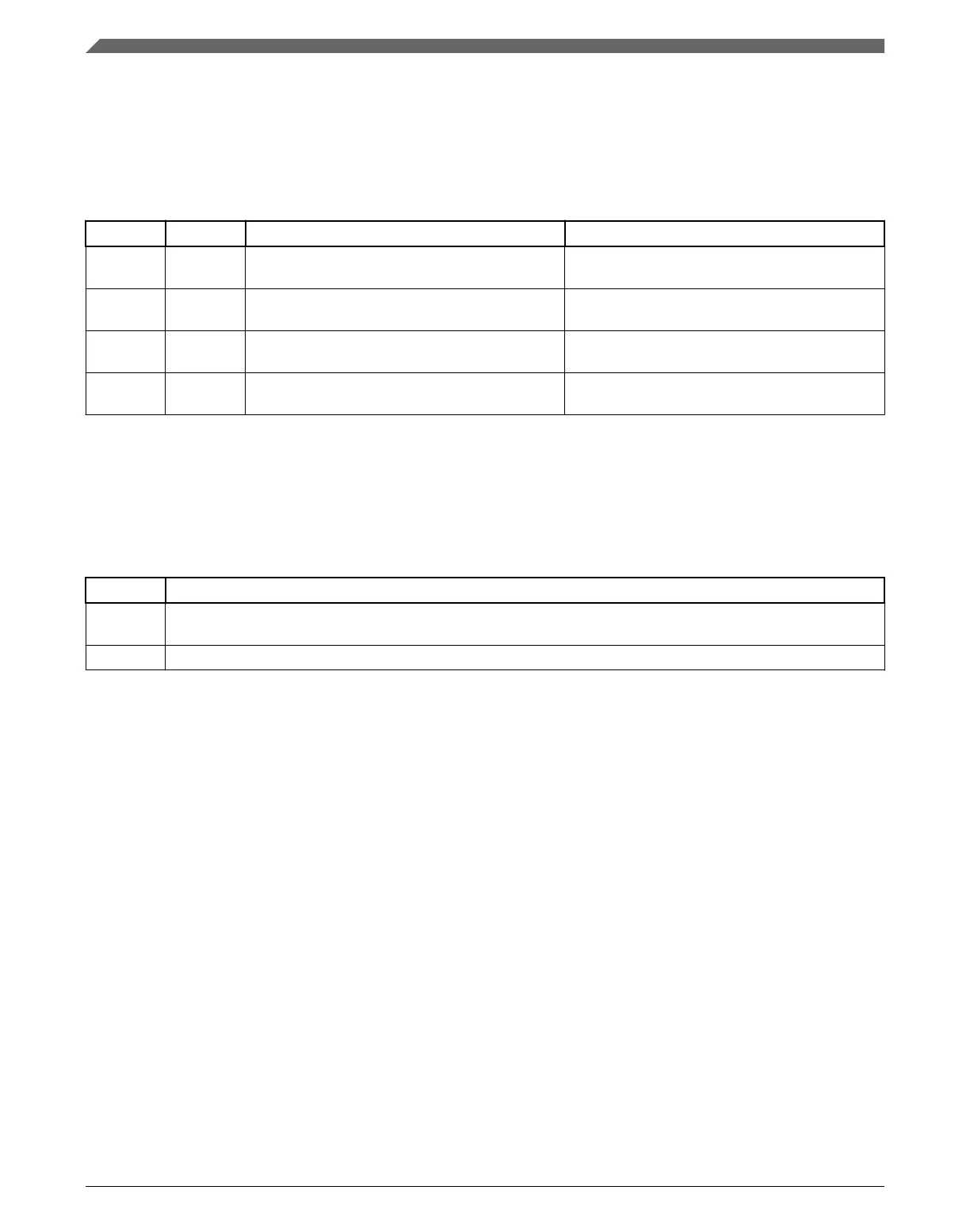

If DMA = 1, the CHnF bit is cleared either by channel DMA transfer done or reading

CnSC while CHnF is set and then writing a zero to CHnF bit according to CHnIE bit. See

the following table.

Table 39-14. Clear CHnF bit when DMA = 1

CHnIE How CHnF Bit Can Be Cleared

0 CHnF bit is cleared either when the channel DMA transfer is done or by reading CnSC while CHnF is set and

then writing a 0 to CHnF bit.

1 CHnF bit is cleared when the channel DMA transfer is done.

39.4.24 Dual Edge Capture mode

The Dual Edge Capture mode is selected if DECAPEN = 1. This mode allows to measure

a pulse width or period of the signal on the input of channel (n) of a channel pair. The

channel (n) filter can be active in this mode when n is 0 or 2.

Functional description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1006 NXP Semiconductors

Loading...

Loading...