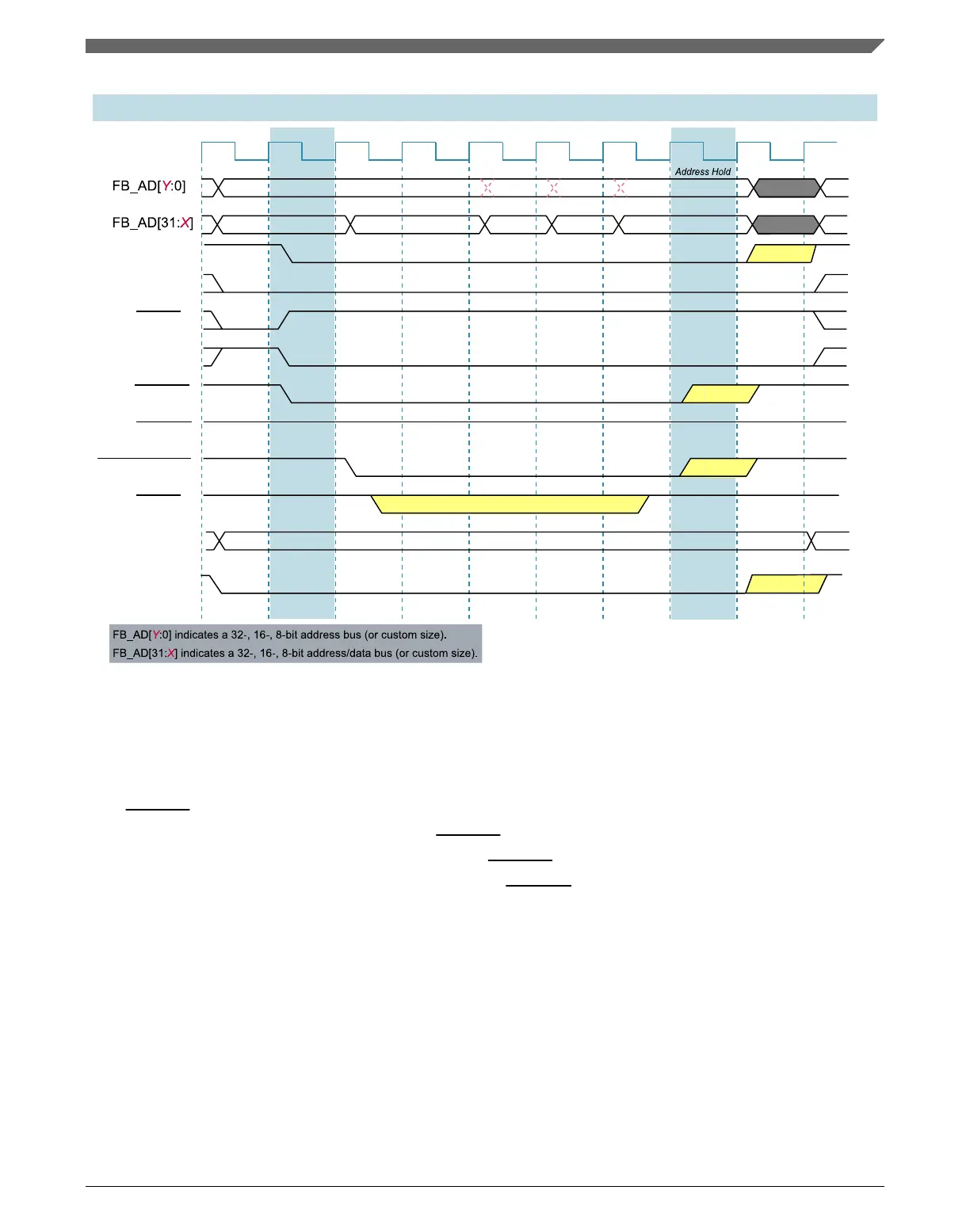

Address

Address

Data Data Data Data

Add+1 Add+2

Add+3

FB_CLK

TSIZ=00

AA=1

AA=1

AA=0

FB_RW

FB_TS

FB_ALE

FB_TBST

FB_OEn

FB_BE/BWEn

FB_TA

FB_TSIZ[1:0]

32-bit Write Burst to 8-bit port 3-1-1-1, with Address Setup and Hold

AA=0

FB_CSn

AA=0

S0 AS S2 S2 S2 S2 AH S3 S0

Address Setup

Write32bBurst3111ASAH.svg

If AA=1, the address increments

If AA=0, the address stays the same

S1

S0 AS S2 S2 S2 S2 AH S3 S0S1

TIP

AA=1

AA=1

AA=0

Figure 31-28. 32-bit-write burst to 8-bit port 3-1-1-1 (address setup and hold)

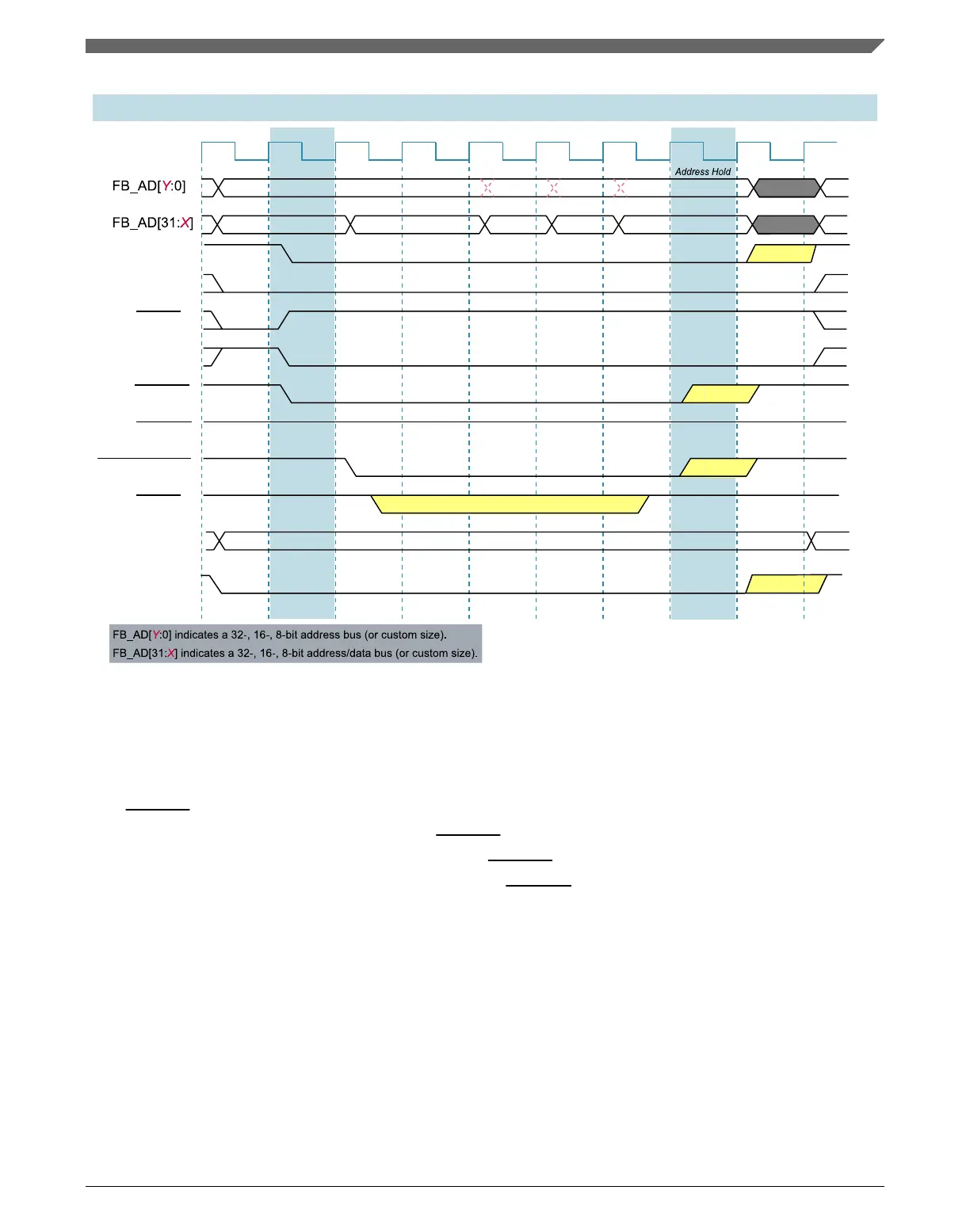

31.4.13

Extended Transfer Start/Address Latch Enable

The FB_TS/FB_ALE signal indicates that a bus transaction has begun and the address

and attributes are valid. By default, the FB_TS/FB_ALE signal asserts for a single bus

clock cycle. When CSCRn[EXTS] is set, the

FB_TS/FB_ALE signal asserts and remain

asserted until the first positive clock edge after FB_CSn asserts. See the following figure.

NOTE

When EXTS is set, CSCRn[WS] must be programmed to have

at least one primary wait state.

Chapter 31 External Bus Interface (FlexBus)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 737

Loading...

Loading...