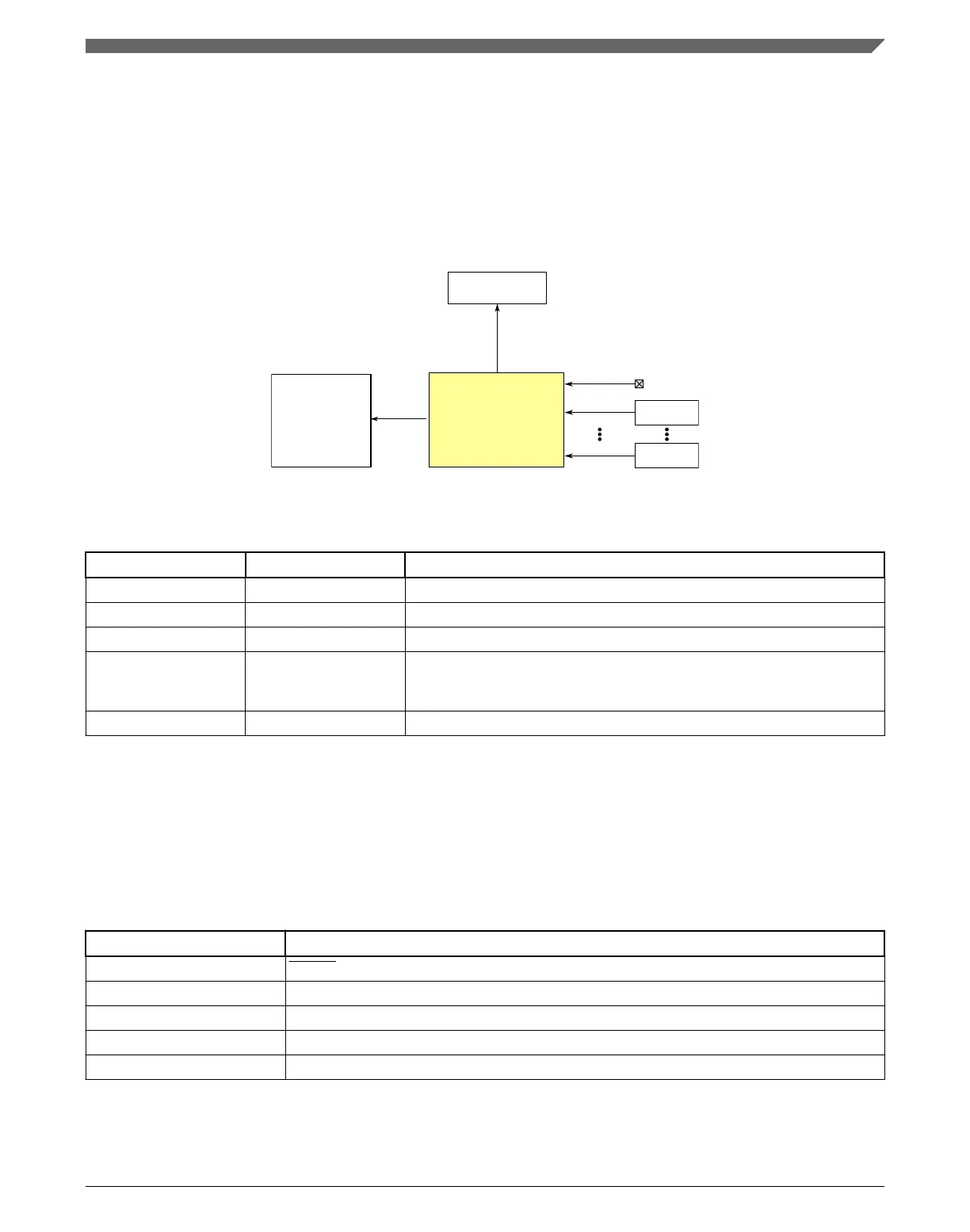

3.2.3 Asynchronous Wake-up Interrupt Controller (AWIC)

Configuration

This section summarizes how the module has been configured in the chip. Full

documentation for this module is provided by ARM and can be found at arm.com.

Asynchronous

Wake-up Interrupt

Controller (AWIC)

Nested vectored

interrupt controller

(NVIC)

Wake-up

requests

Module

Module

Clock logic

Figure 3-3. Asynchronous Wake-up Interrupt Controller configuration

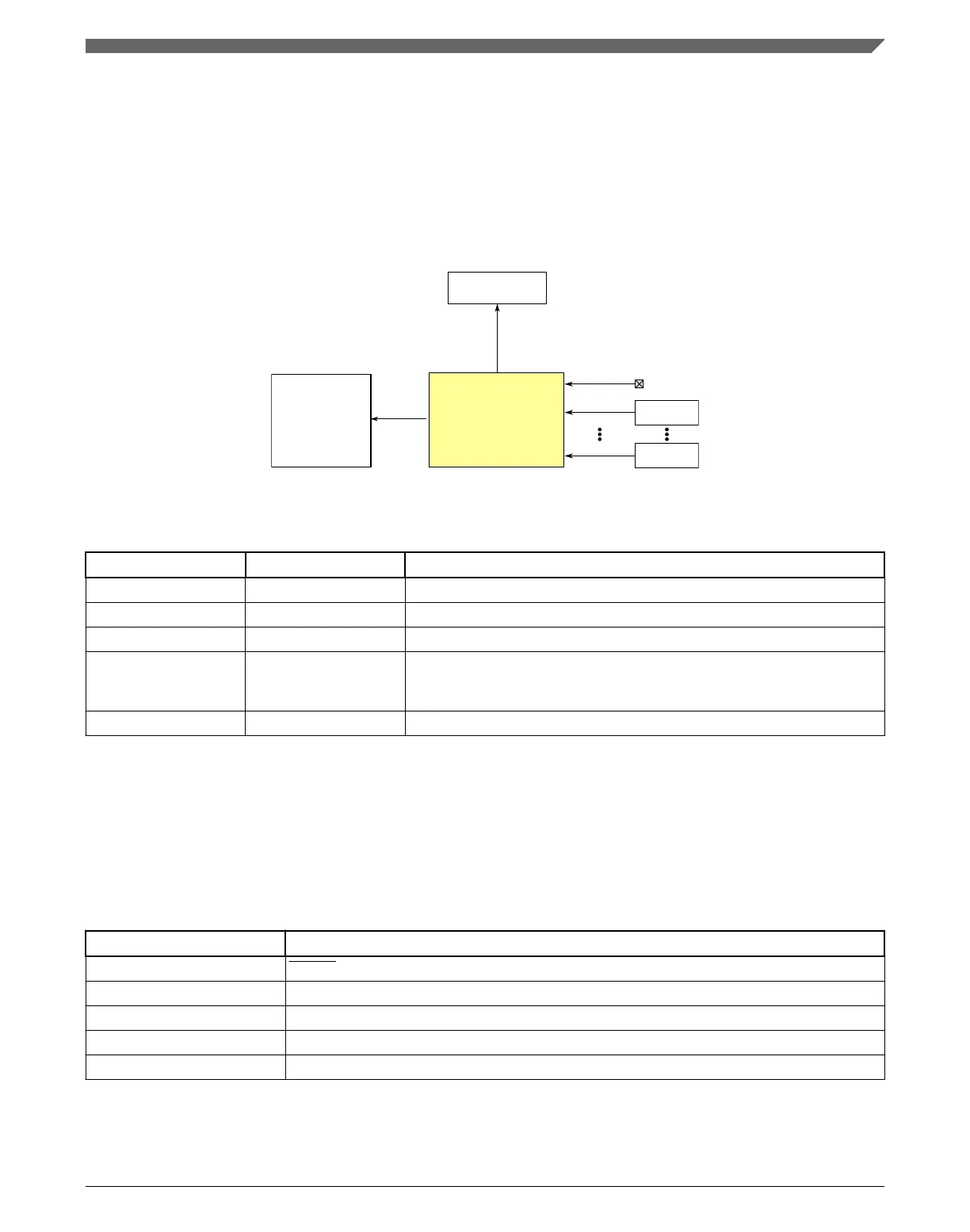

Table 3-6. Reference links to related information

Topic Related module Reference

System memory map System memory map

Clocking Clock distribution

Power management Power management

Nested Vectored

Interrupt Controller

(NVIC)

NVIC

Wake-up requests AWIC wake-up sources

3.2.3.1 Wake-up sources

The device uses the following internal and external inputs to the AWIC module.

Table 3-7. AWIC Partial Stop, Stop and VLPS Wake-up Sources

Wake-up source Description

Available system resets RESET pin and WDOG when LPO is its clock source, and JTAG

Low-voltage detect Power Mode Controller

Low-voltage warning Power Mode Controller

Pin interrupts Port Control Module - Any enabled pin interrupt is capable of waking the system

ADCx The ADC is functional when using internal clock source

Table continues on the next page...

Chapter 3 Chip Configuration

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 65

Loading...

Loading...