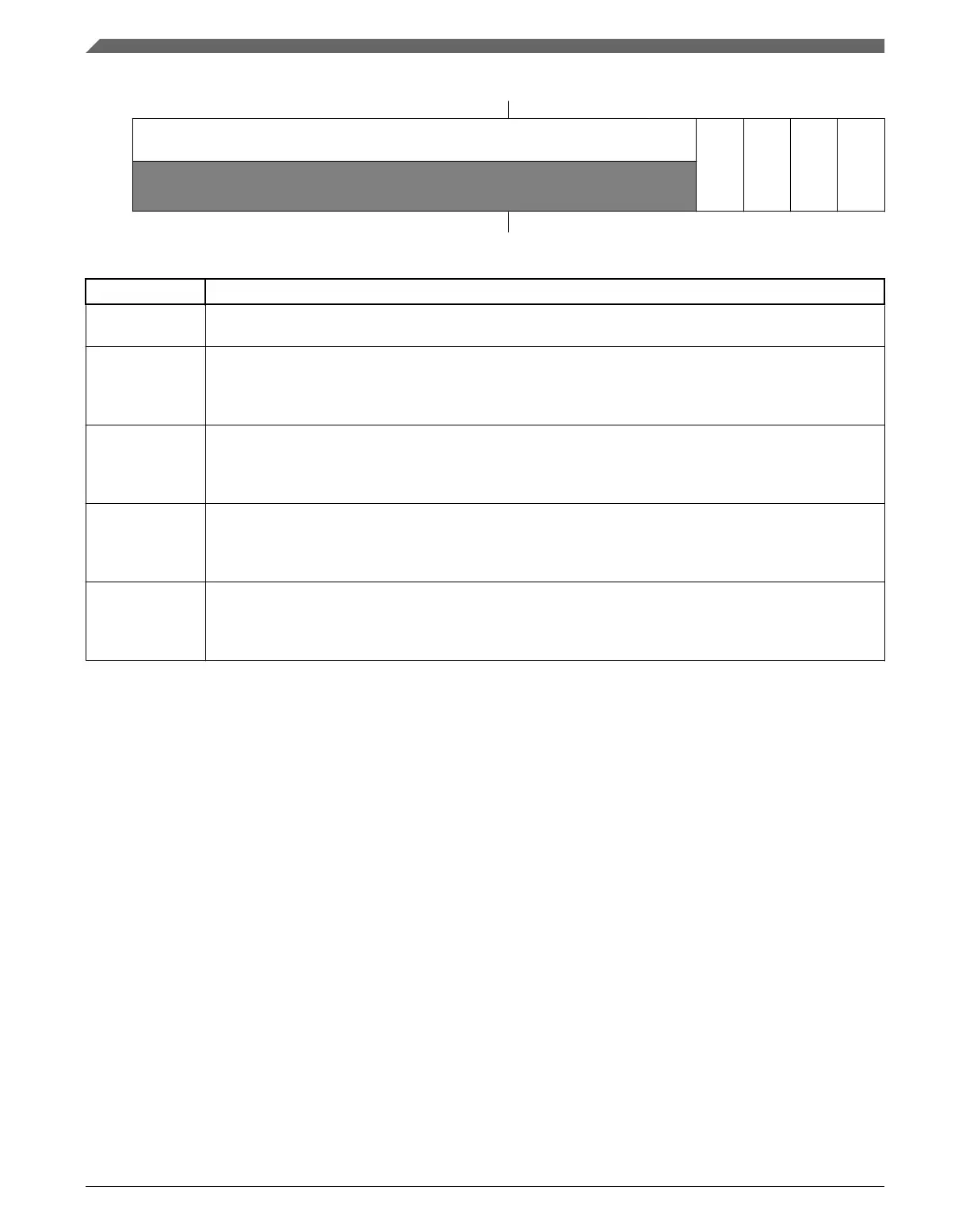

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

INV3EN

INV2EN

INV1EN

INV0EN

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

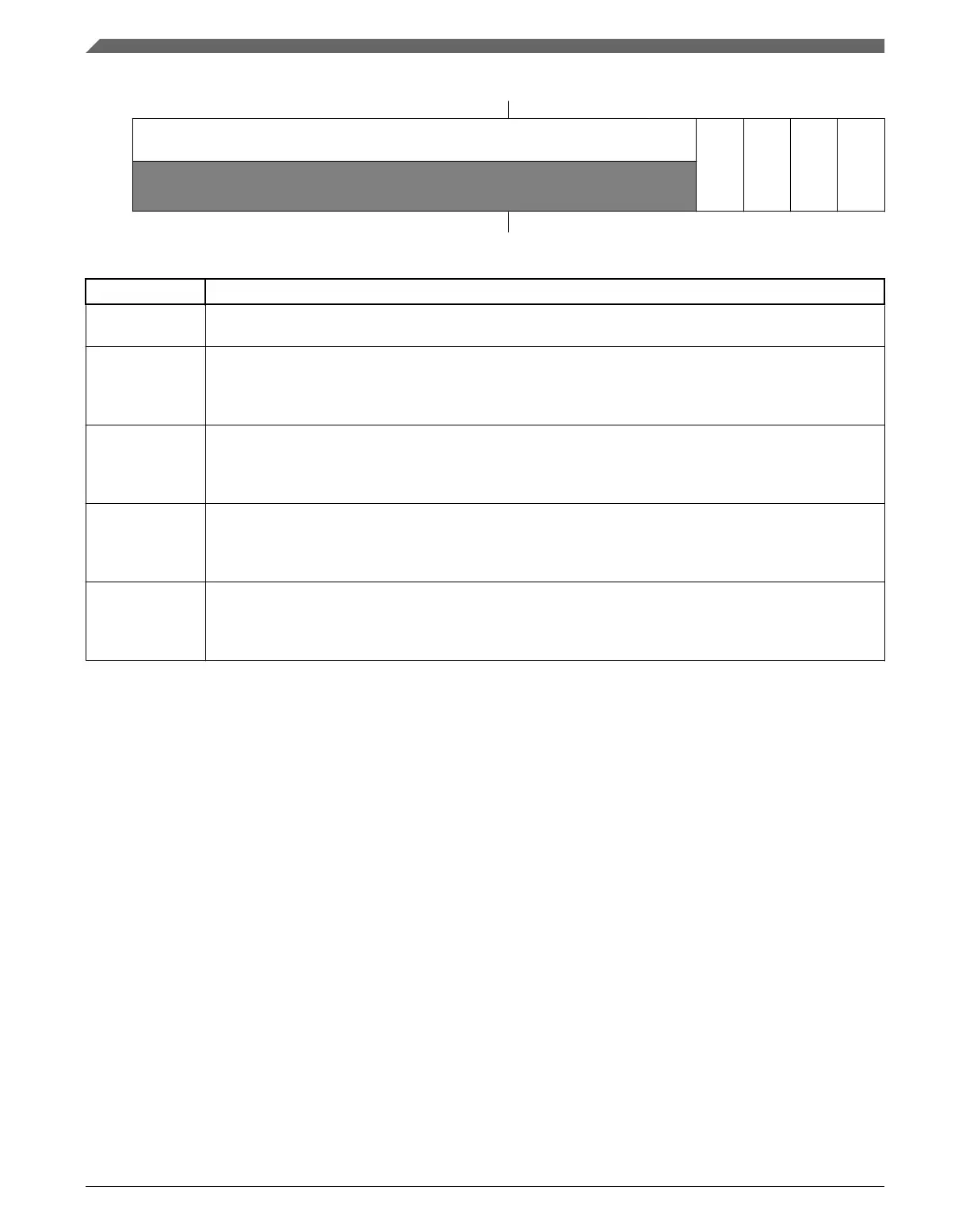

FTMx_INVCTRL field descriptions

Field Description

31–4

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

3

INV3EN

Pair Channels 3 Inverting Enable

0 Inverting is disabled.

1 Inverting is enabled.

2

INV2EN

Pair Channels 2 Inverting Enable

0 Inverting is disabled.

1 Inverting is enabled.

1

INV1EN

Pair Channels 1 Inverting Enable

0 Inverting is disabled.

1 Inverting is enabled.

0

INV0EN

Pair Channels 0 Inverting Enable

0 Inverting is disabled.

1 Inverting is enabled.

39.3.26 FTM Software Output Control (FTMx_SWOCTRL)

This register enables software control of channel (n) output and defines the value forced

to the channel (n) output:

• The CHnOC bits enable the control of the corresponding channel (n) output by

software.

• The CHnOCV bits select the value that is forced at the corresponding channel (n)

output.

This register has a write buffer. The fields are updated by the SWOCTRL register

synchronization.

Memory map and register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

942 NXP Semiconductors

Loading...

Loading...