MCG_C7 field descriptions

Field Description

7–6

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

5–2

Reserved

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

OSCSEL MCG OSC Clock Select

Selects the MCG FLL external reference clock

NOTE:

The OSCSEL field can’t be changed during MCG modes (like PBE), when external clock is

serving as the clock source for MCG.

00 Selects Oscillator (OSCCLK0).

01 Selects 32 kHz RTC Oscillator.

10 Selects Oscillator (OSCCLK1).

11 RESERVED

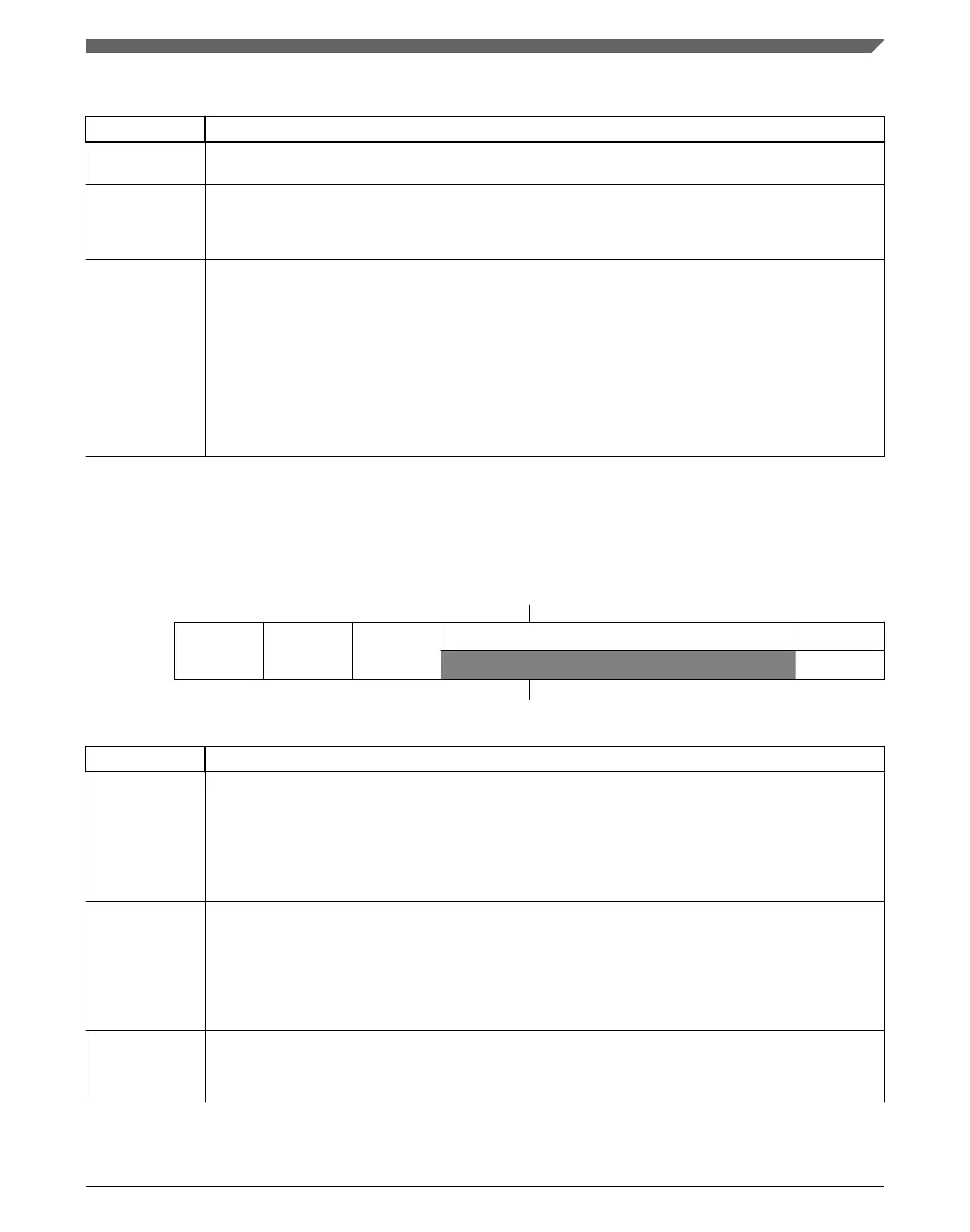

25.3.12 MCG Control 8 Register (MCG_C8)

Address: 4006_4000h base + Dh offset = 4006_400Dh

Bit 7 6 5 4 3 2 1 0

Read

LOCRE1 LOLRE CME1

0 LOCS1

Write w1c

Reset

1 0 0 0 0 0 0 0

MCG_C8 field descriptions

Field Description

7

LOCRE1

Loss of Clock Reset Enable

Determines if a interrupt or a reset request is made following a loss of RTC external reference clock. The

LOCRE1 only has an affect when CME1 is set.

0 Interrupt request is generated on a loss of RTC external reference clock.

1 Generate a reset request on a loss of RTC external reference clock

6

LOLRE

PLL Loss of Lock Reset Enable

Determines if an interrupt or a reset request is made following a PLL loss of lock.

0 Interrupt request is generated on a PLL loss of lock indication. The PLL loss of lock interrupt enable bit

must also be set to generate the interrupt request.

1 Generate a reset request on a PLL loss of lock indication.

5

CME1

Clock Monitor Enable1

Enables the loss of clock monitoring circuit for the output of the RTC external reference clock. The

LOCRE1 bit will determine whether an interrupt or a reset request is generated following a loss of RTC

Table continues on the next page...

Chapter 25 Multipurpose Clock Generator (MCG)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 555

Loading...

Loading...