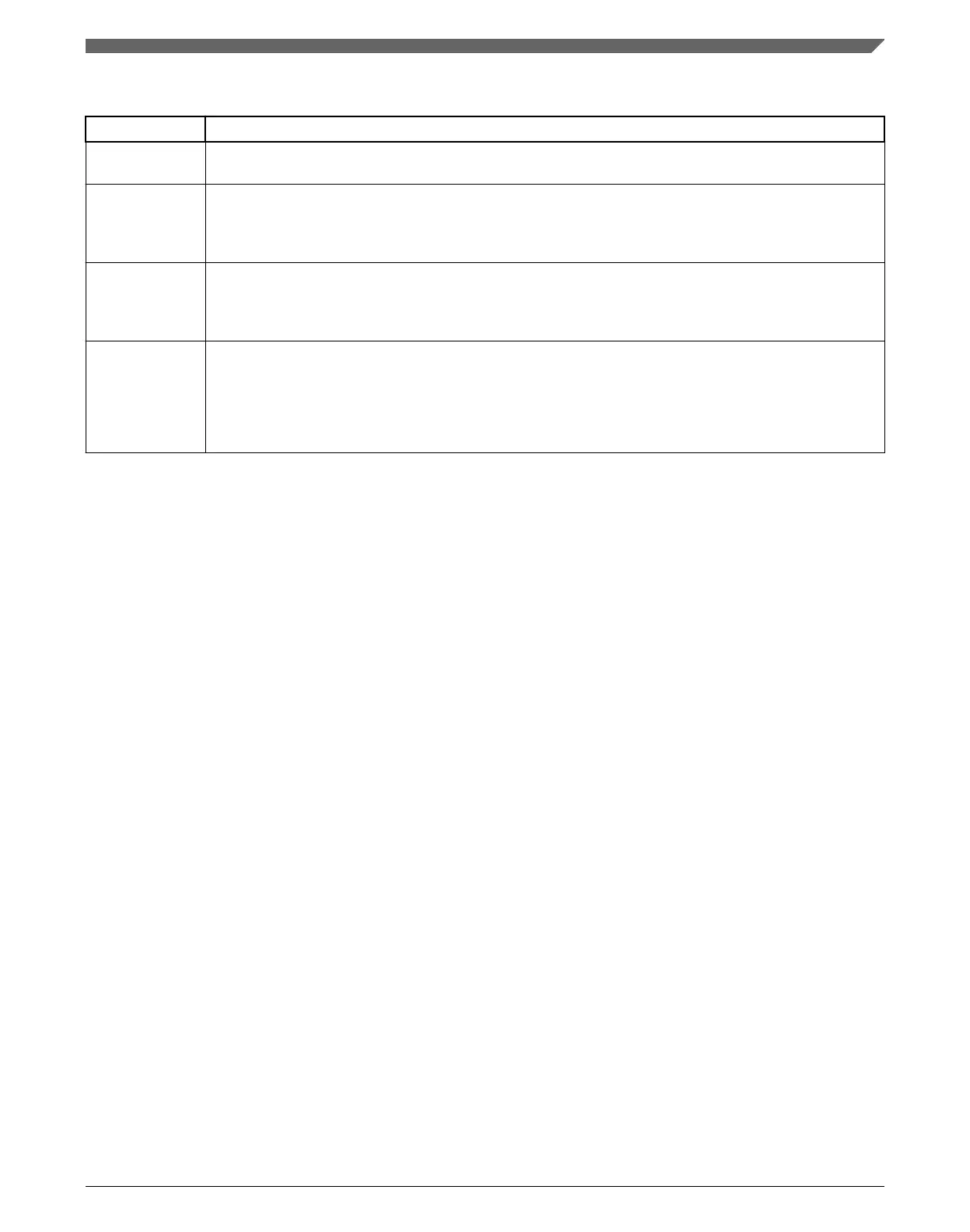

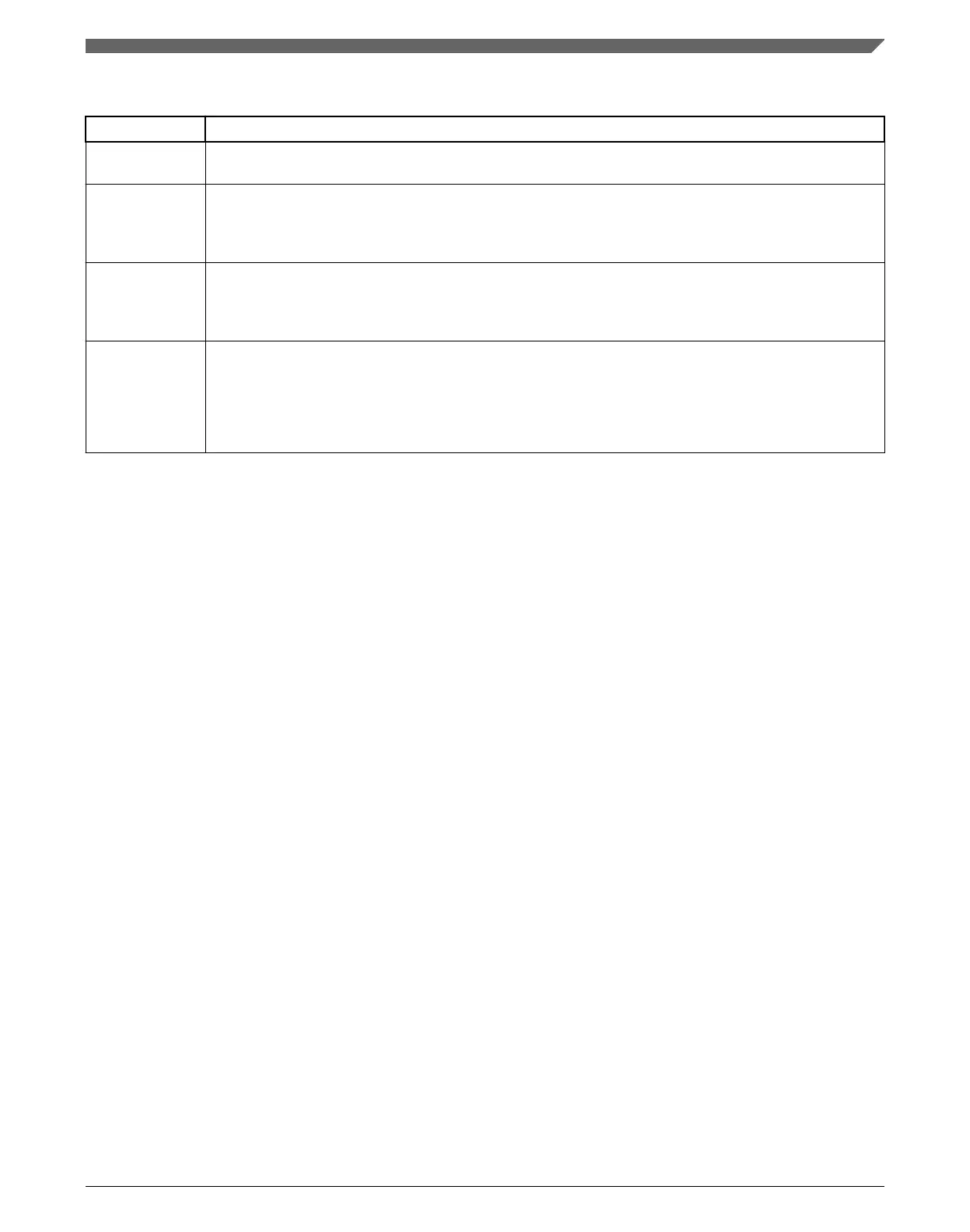

MCM_CPO field descriptions

Field Description

31–3

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

2

CPOWOI

Compute Operation wakeup on interrupt

0 No effect.

1 When set, the CPOREQ is cleared on any interrupt or exception vector fetch.

1

CPOACK

Compute Operation acknowledge

0 Compute operation entry has not completed or compute operation exit has completed.

1 Compute operation entry has completed or compute operation exit has not completed.

0

CPOREQ

Compute Operation request

This bit is auto-cleared by vector fetching if CPOWOI = 1.

0 Request is cleared.

1 Request Compute Operation.

18.3 Functional description

This section describes the functional description of MCM module.

18.3.1

Interrupts

The MCM's interrupt is generated if any of the following is true:

• FPU input denormal interrupt is enabled (FIDCE) and an input is denormalized

(FIDC)

• FPU inexact interrupt is enabled (FIXCE) and a number is inexact (FIXC)

• FPU underflow interrupt is enabled (FUFCE) and an underflow occurs (FUFC)

• FPU overflow interrupt is enabled (FOFCE) and an overflow occurs (FOFC)

• FPU divide-by-zero interrupt is enabled (FDZCE) and a divide-by-zero occurs

(FDZC)

• FPU invalid operation interrupt is enabled (FDZCE) and an invalid occurs (FDZC)

18.3.1.1

Determining source of the interrupt

To determine the exact source of the interrupt qualify the interrupt status flags with the

corresponding interrupt enable bits.

1. From MCM_ISCR[31:16] && MCM_ISCR[15:0]

Chapter 18 Miscellaneous Control Module (MCM)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 405

Loading...

Loading...