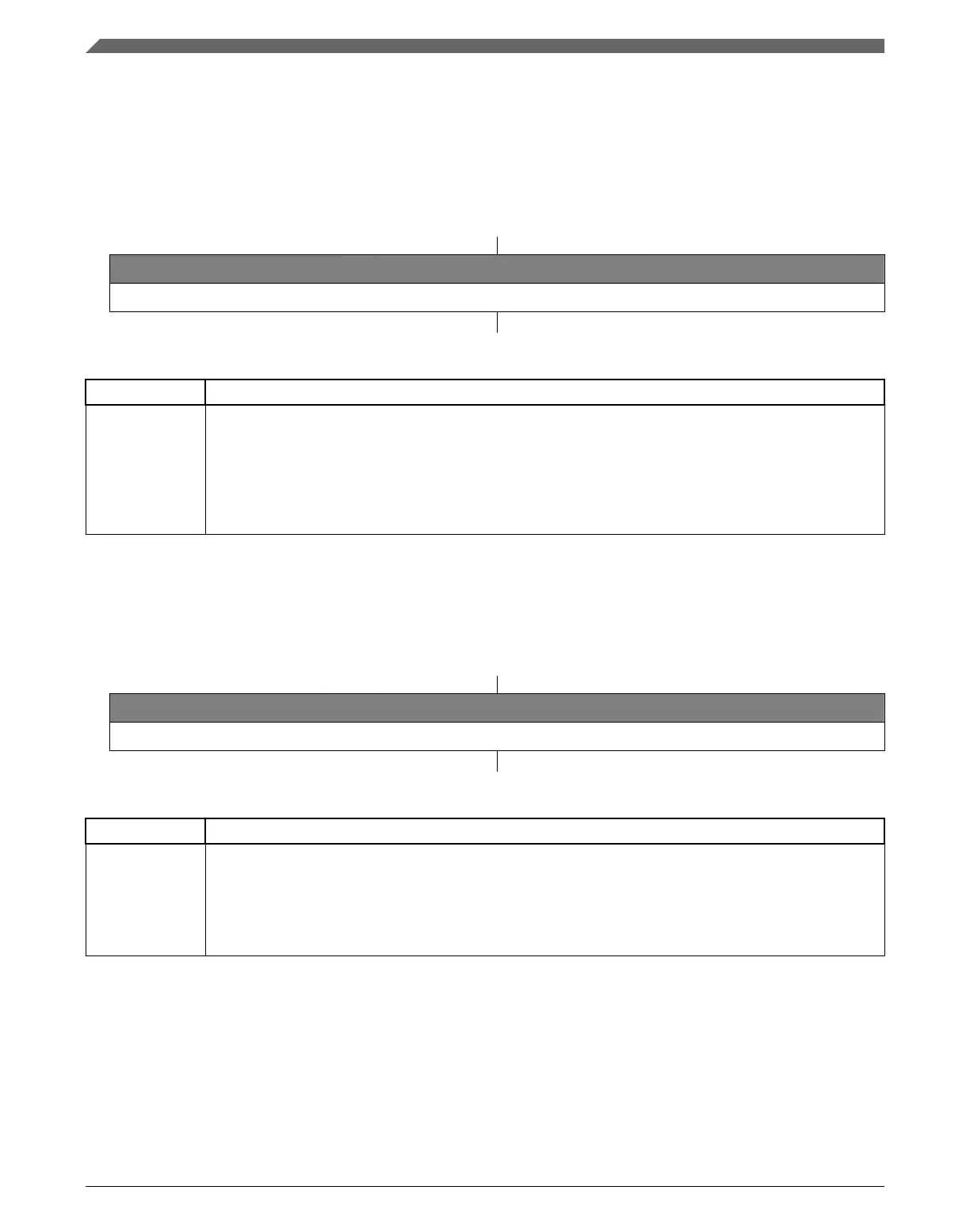

50.2.3 Port Clear Output Register (GPIOx_PCOR)

This register configures whether to clear the fields of PDOR.

Address: Base address + 8h offset

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

W

PTCO

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

GPIOx_PCOR field descriptions

Field Description

PTCO Port Clear Output

Writing to this register will update the contents of the corresponding bit in the Port Data Output Register

(PDOR) as follows:

0 Corresponding bit in PDORn does not change.

1 Corresponding bit in PDORn is cleared to logic 0.

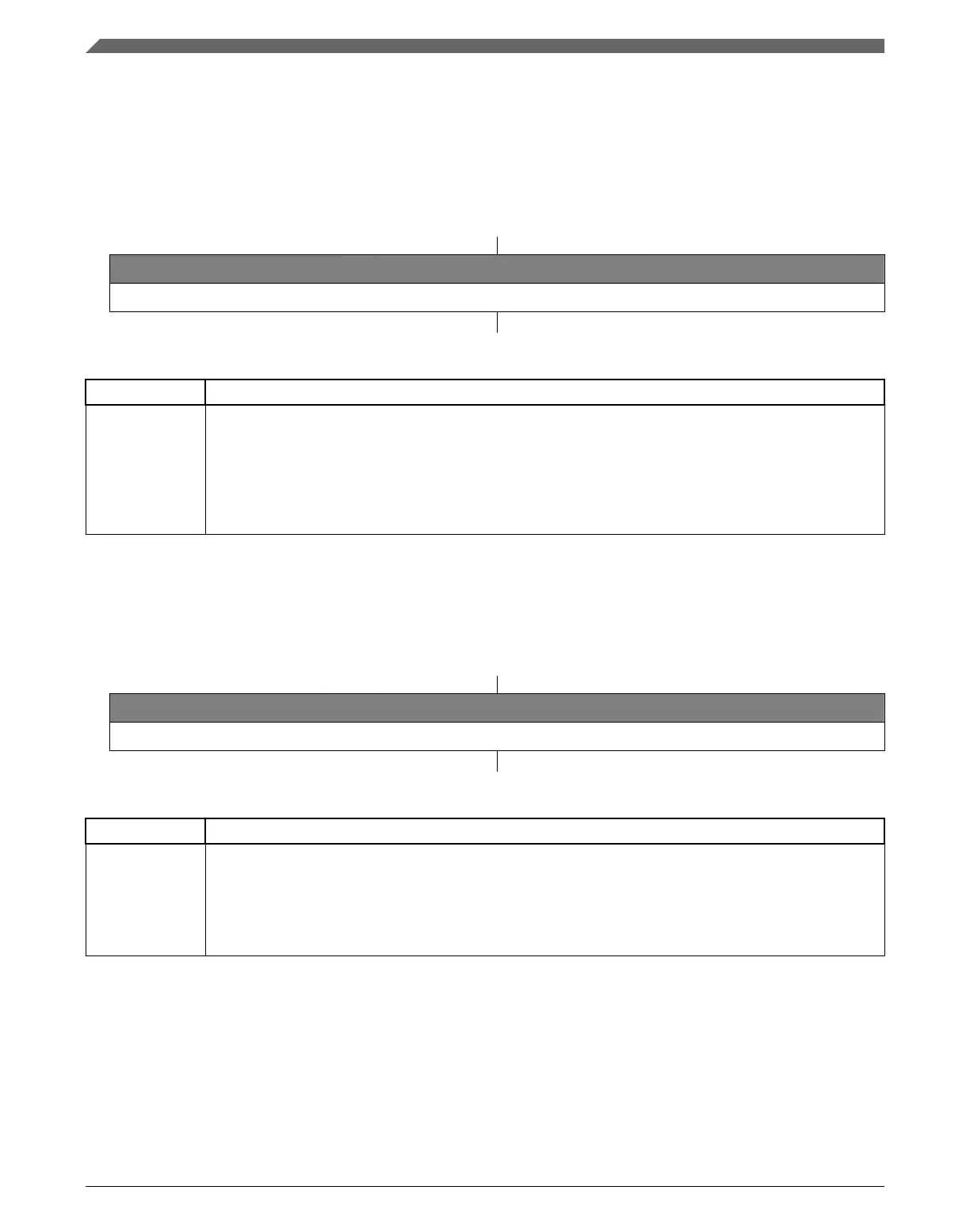

50.2.4 Port Toggle Output Register (GPIOx_PTOR)

Address: Base address + Ch offset

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

W

PTTO

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

GPIOx_PTOR field descriptions

Field Description

PTTO Port Toggle Output

Writing to this register will update the contents of the corresponding bit in the PDOR as follows:

0 Corresponding bit in PDORn does not change.

1 Corresponding bit in PDORn is set to the inverse of its existing logic state.

Memory map and register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1380 NXP Semiconductors

Loading...

Loading...