48.2.4 LPUART Data Register (LPUARTx_DATA)

This register is actually two separate registers. Reads return the contents of the read-only

receive data buffer and writes go to the write-only transmit data buffer. Reads and writes

of this register are also involved in the automatic flag clearing mechanisms for some of

the LPUART status flags.

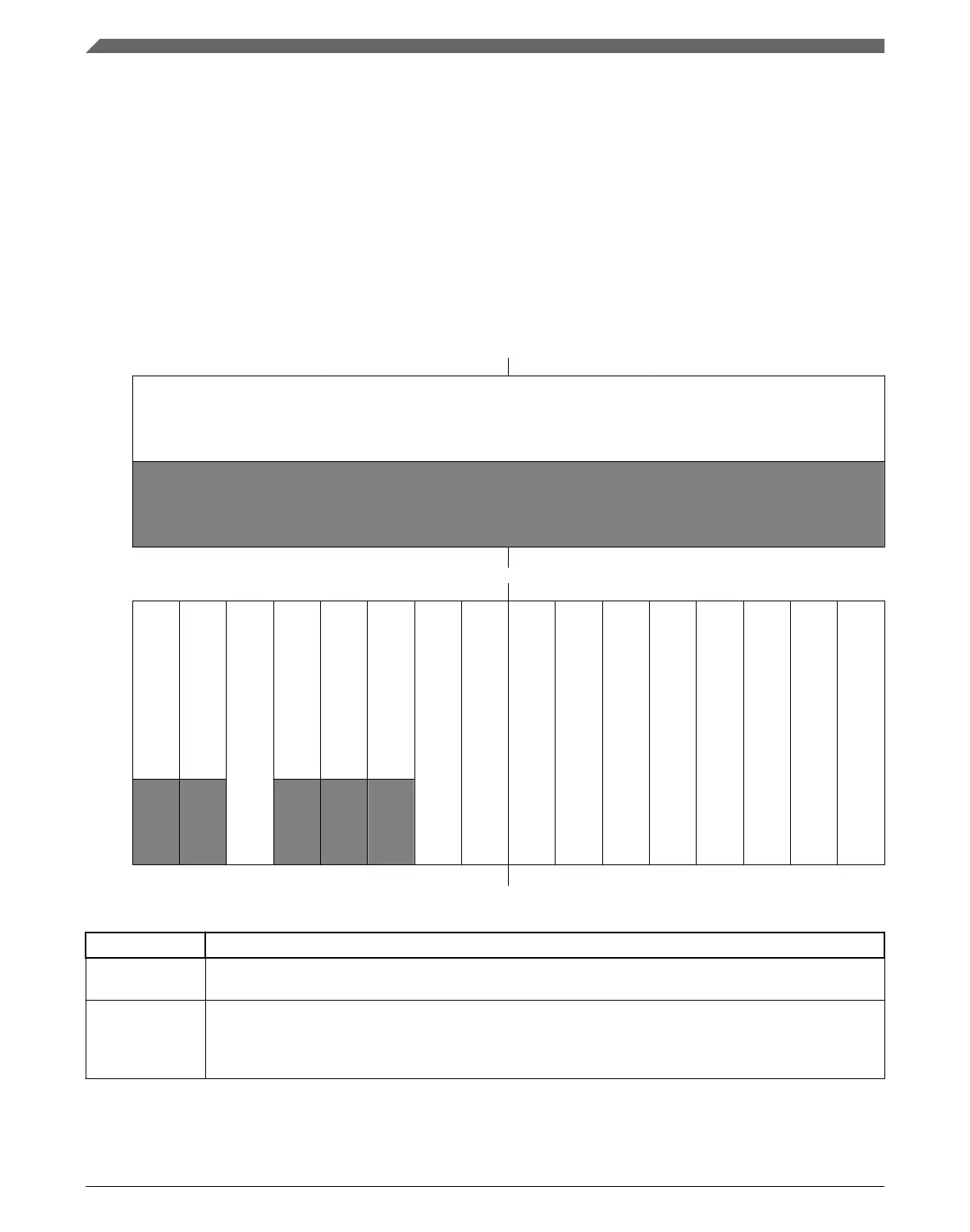

Address:

4002_A000h base + Ch offset = 4002_A00Ch

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

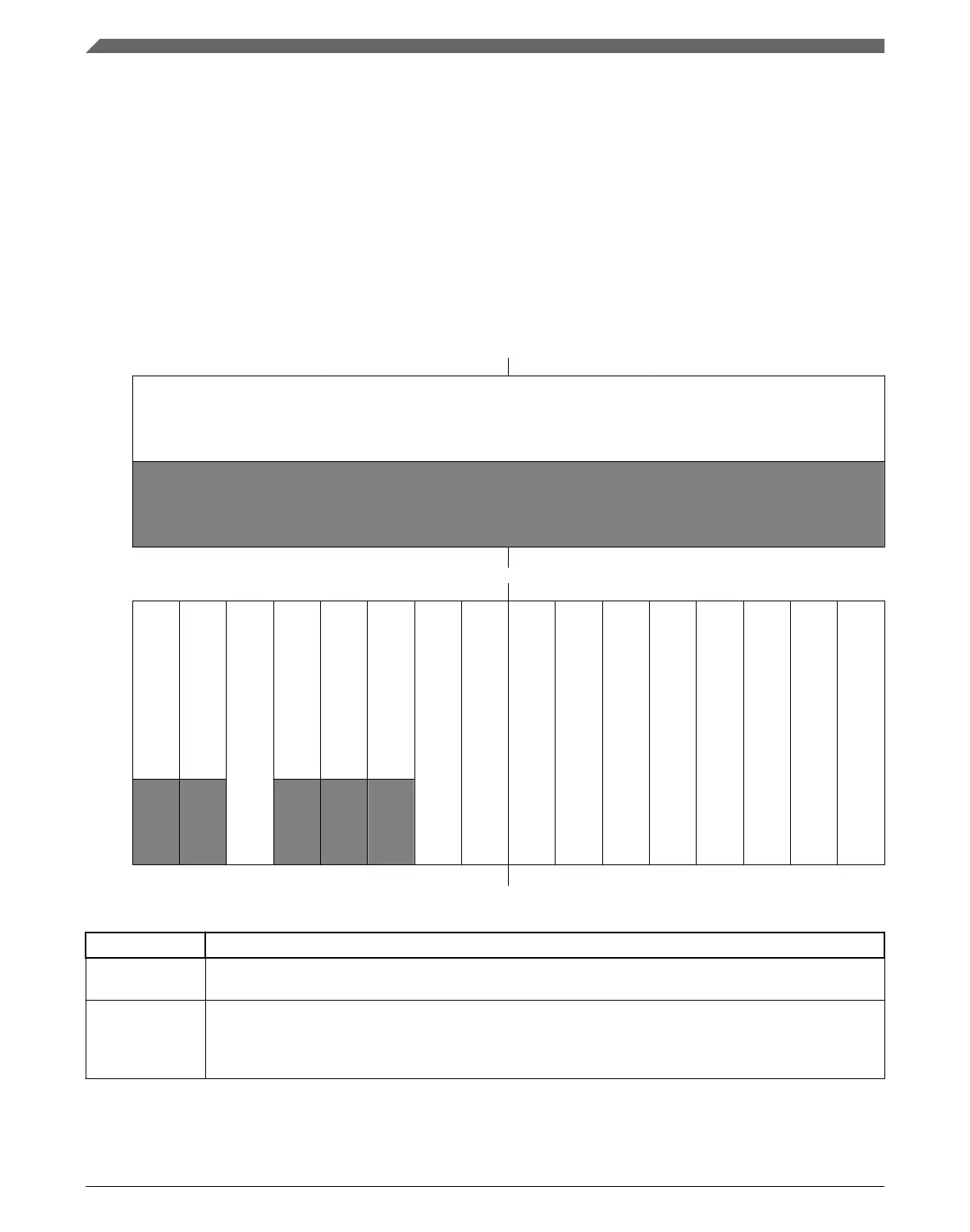

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

NOISY

PARITYE

FRETSC

RXEMPT

IDLINE

0

R9T9 R8T8 R7T7 R6T6 R5T5 R4T4 R3T3 R2T2 R1T1 R0T0

W

Reset

0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0

LPUARTx_DATA field descriptions

Field Description

31–16

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

15

NOISY

The current received dataword contained in DATA[R9:R0] was received with noise.

0 The dataword was received without noise.

1 The data was received with noise.

Table continues on the next page...

Register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1318 NXP Semiconductors

Loading...

Loading...