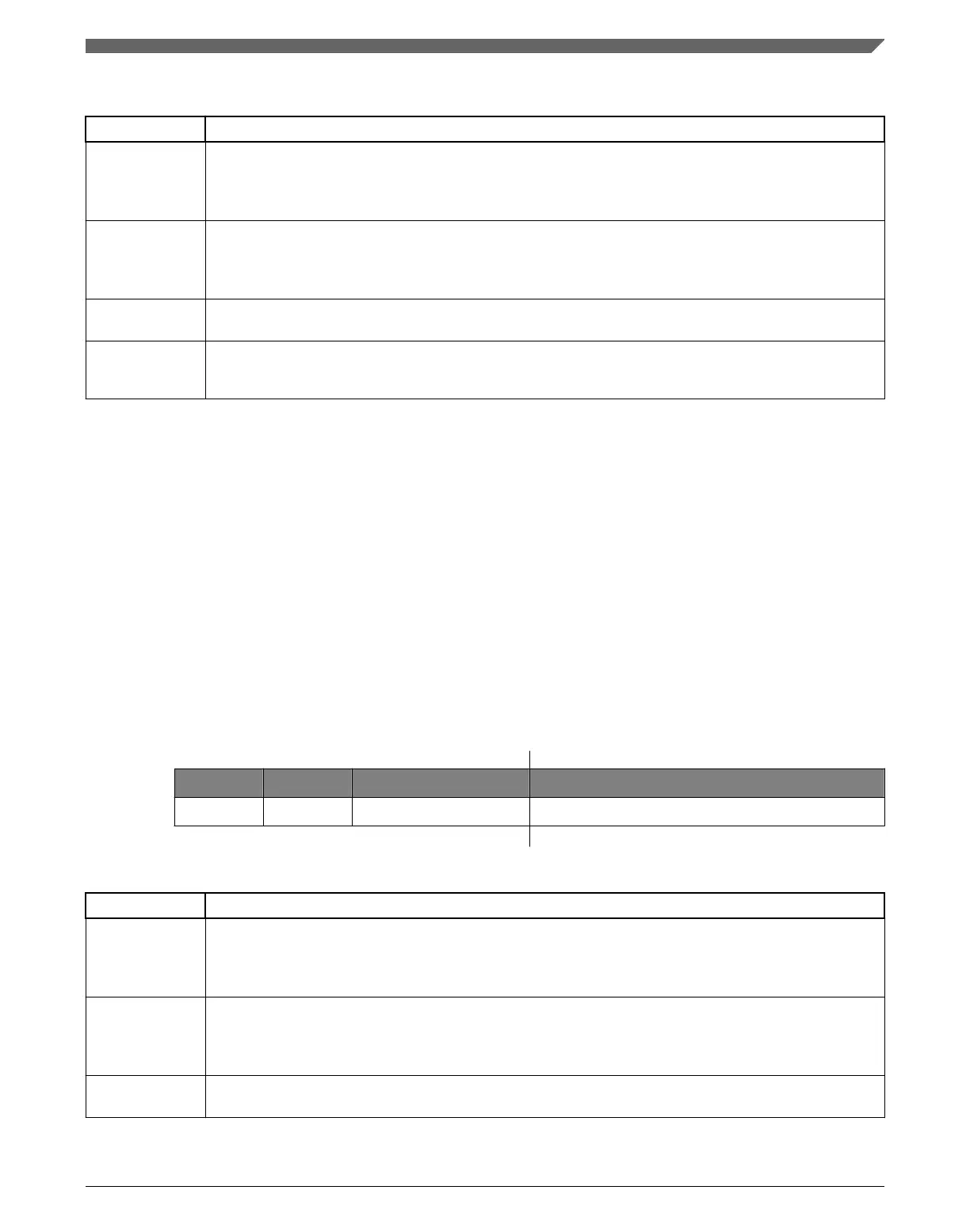

DMA_CEEI field descriptions

Field Description

7

NOP

No Op enable

0 Normal operation

1 No operation, ignore the other bits in this register

6

CAEE

Clear All Enable Error Interrupts

0 Clear only the EEI bit specified in the CEEI field

1 Clear all bits in EEI

5–4

Reserved

This field is reserved.

CEEI Clear Enable Error Interrupt

Clears the corresponding bit in EEI

22.3.10 Set Enable Error Interrupt Register (DMA_SEEI)

The SEEI provides a simple memory-mapped mechanism to set a given bit in the EEI to

enable the error interrupt for a given channel. The data value on a register write causes

the corresponding bit in the EEI to be set. Setting the SAEE bit provides a global set

function, forcing the entire EEI contents to be set. If the NOP bit is set, the command is

ignored. This allows you to write multiple-byte registers as a 32-bit word. Reads of this

register return all zeroes.

Address:

4000_8000h base + 19h offset = 4000_8019h

Bit 7 6 5 4 3 2 1 0

Read 0 0 0

Write NOP SAEE 0 SEEI

Reset

0 0 0 0 0 0 0 0

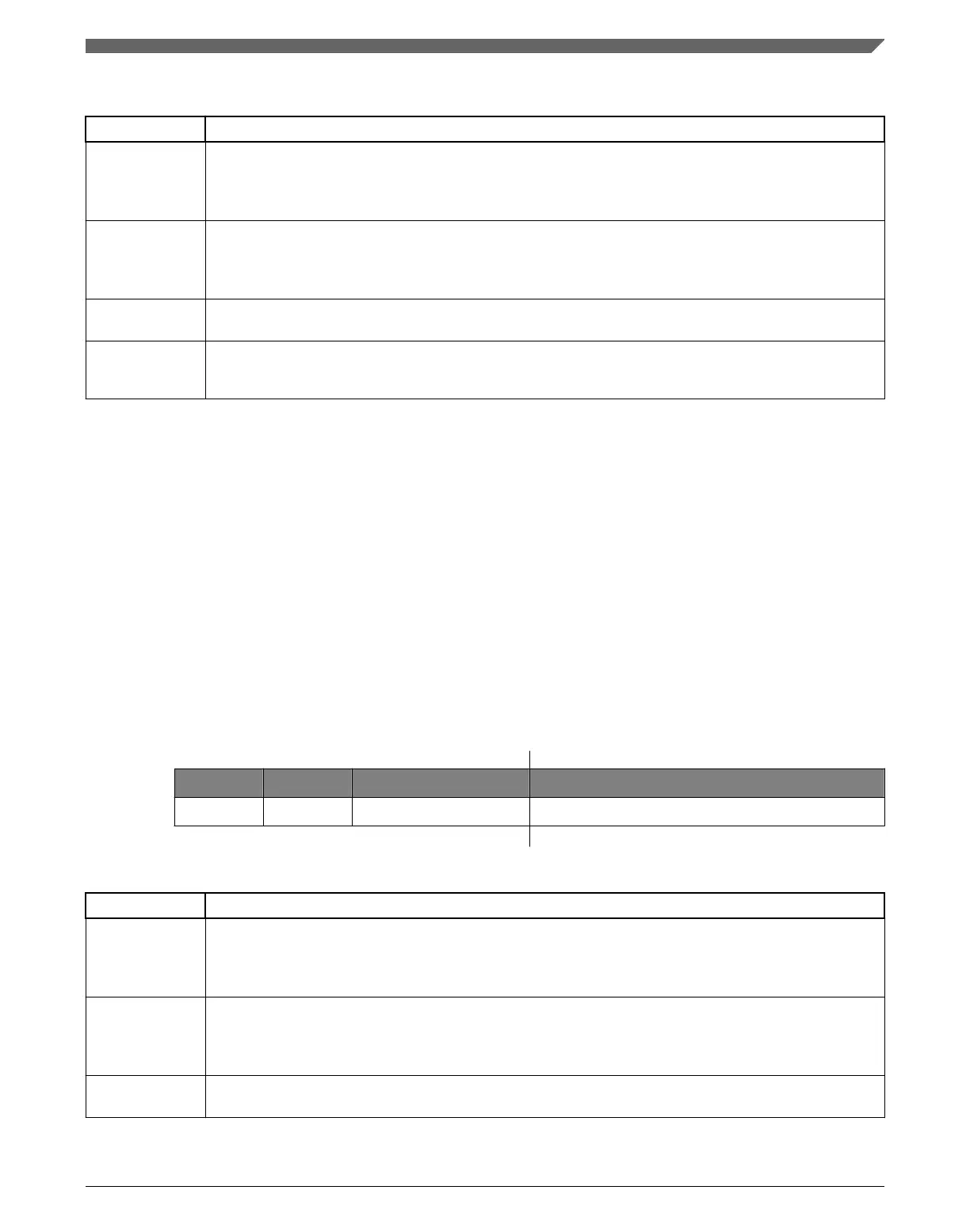

DMA_SEEI field descriptions

Field Description

7

NOP

No Op enable

0 Normal operation

1 No operation, ignore the other bits in this register

6

SAEE

Sets All Enable Error Interrupts

0 Set only the EEI bit specified in the SEEI field.

1 Sets all bits in EEI

5–4

Reserved

This field is reserved.

Table continues on the next page...

Chapter 22 Enhanced Direct Memory Access (eDMA)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 451

Loading...

Loading...