38.3.1 Status and Control register (PDBx_SC)

Address: 4003_6000h base + 0h offset = 4003_6000h

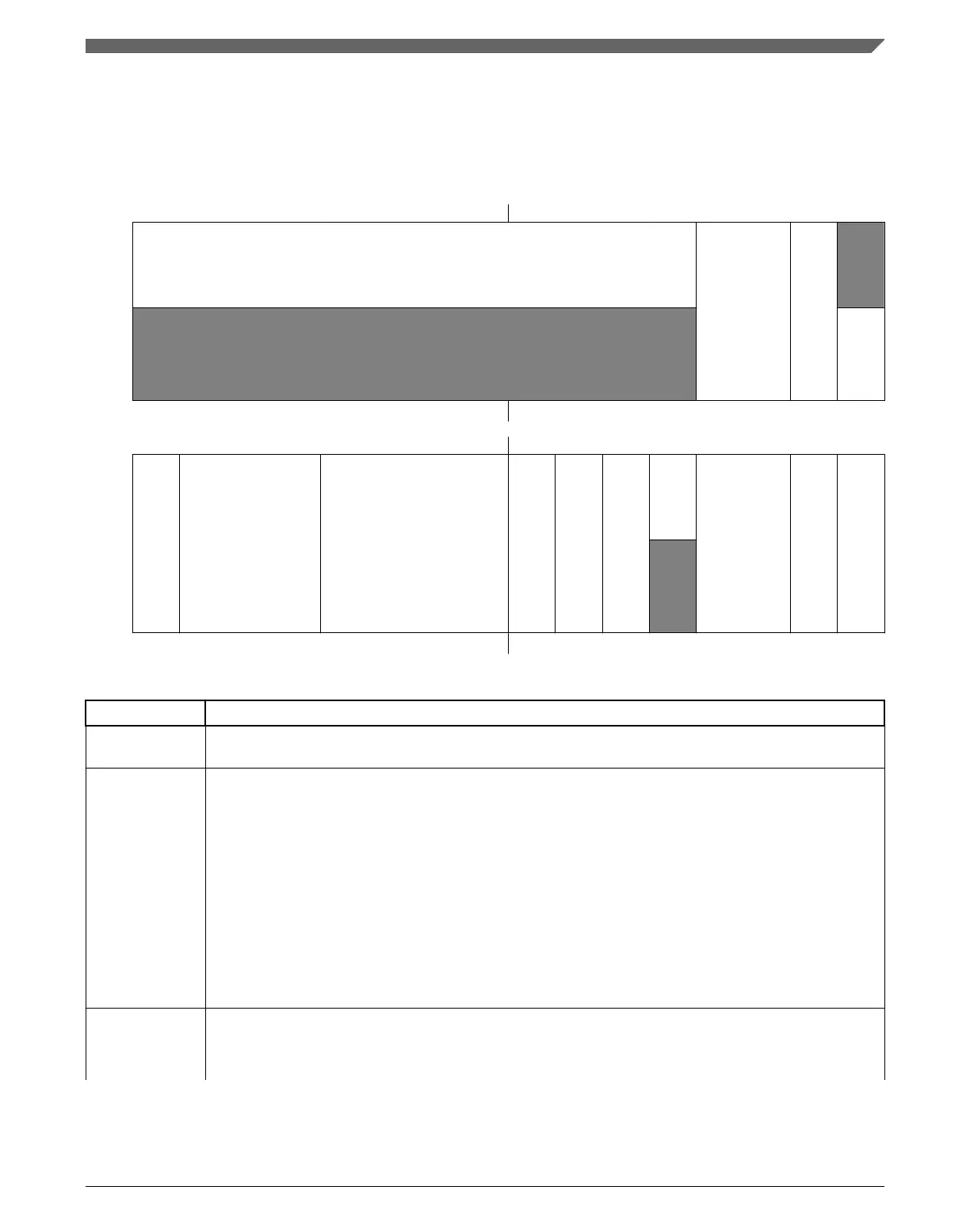

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

0

LDMOD

PDBEIE

0

W

SWTRIG

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

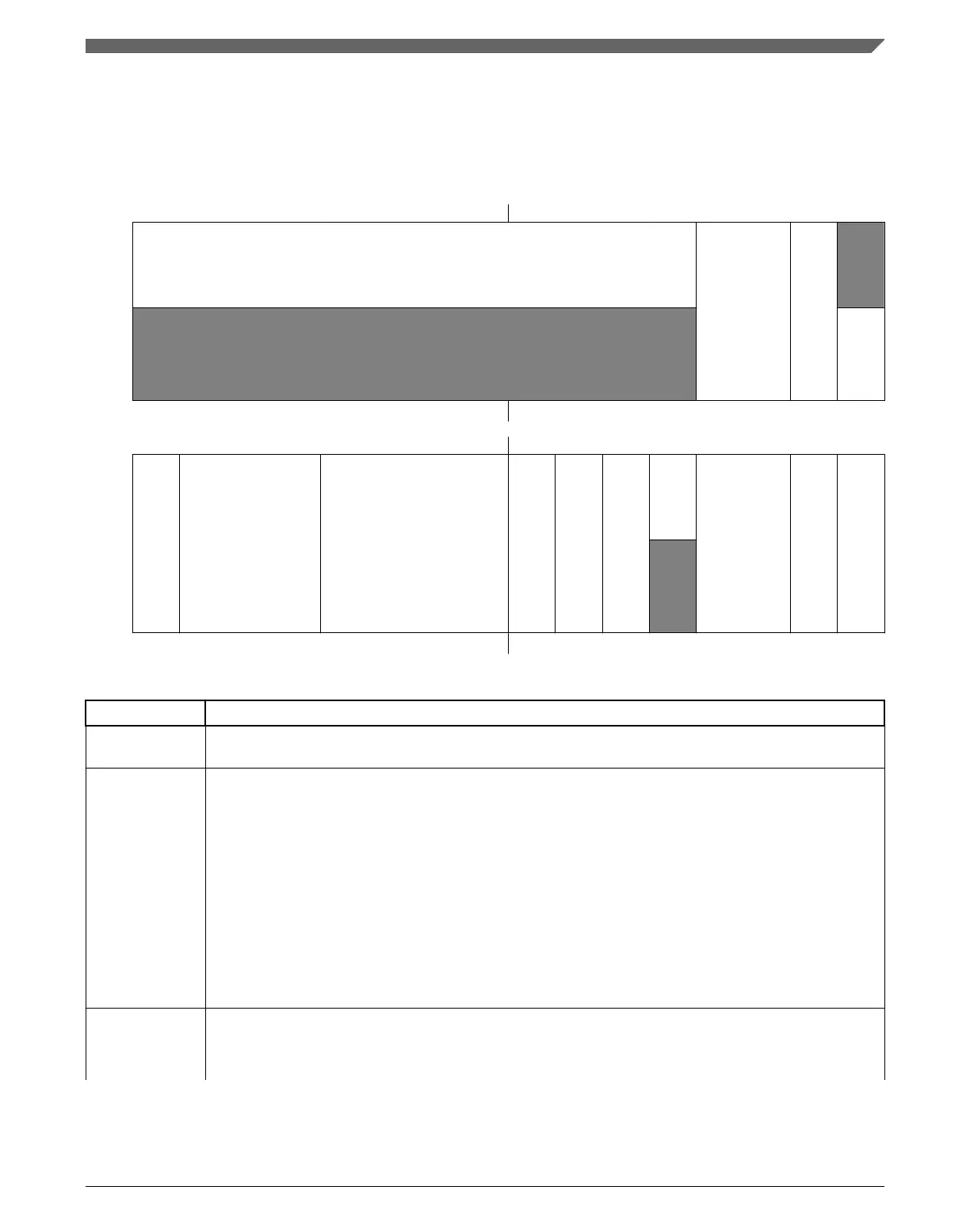

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

DMAEN

PRESCALER TRGSEL

PDBEN

PDBIF

PDBIE

0

MULT

CONT

LDOK

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

PDBx_SC field descriptions

Field Description

31–20

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

19–18

LDMOD

Load Mode Select

Selects the mode to load the MOD, IDLY, CHnDLYm, INTx, and POyDLY registers, after 1 is written to

LDOK.

00 The internal registers are loaded with the values from their buffers immediately after 1 is written to

LDOK.

01 The internal registers are loaded with the values from their buffers when the PDB counter reaches

the MOD register value after 1 is written to LDOK.

10 The internal registers are loaded with the values from their buffers when a trigger input event is

detected after 1 is written to LDOK.

11 The internal registers are loaded with the values from their buffers when either the PDB counter

reaches the MOD register value or a trigger input event is detected, after 1 is written to LDOK.

17

PDBEIE

PDB Sequence Error Interrupt Enable

Enables the PDB sequence error interrupt. When this field is set, any of the PDB channel sequence error

flags generates a PDB sequence error interrupt.

Table continues on the next page...

Chapter 38 Programmable Delay Block (PDB)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 873

Loading...

Loading...