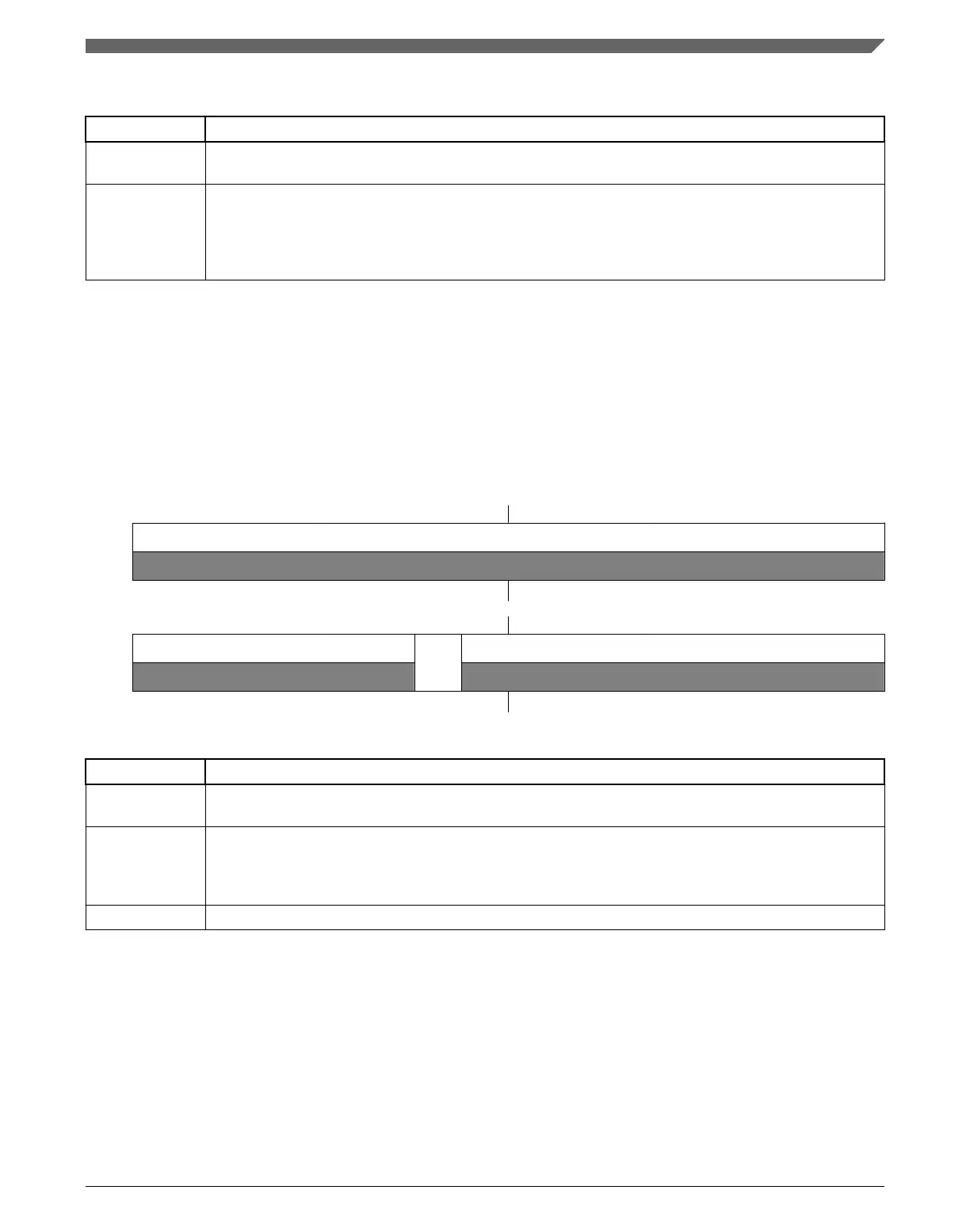

MCM_PLAMC field descriptions

Field Description

15–8

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

AMC Each bit in the AMC field indicates whether there is a corresponding connection to the AXBS master input

port.

0 A bus master connection to AXBS input port n is absent

1 A bus master connection to AXBS input port n is present

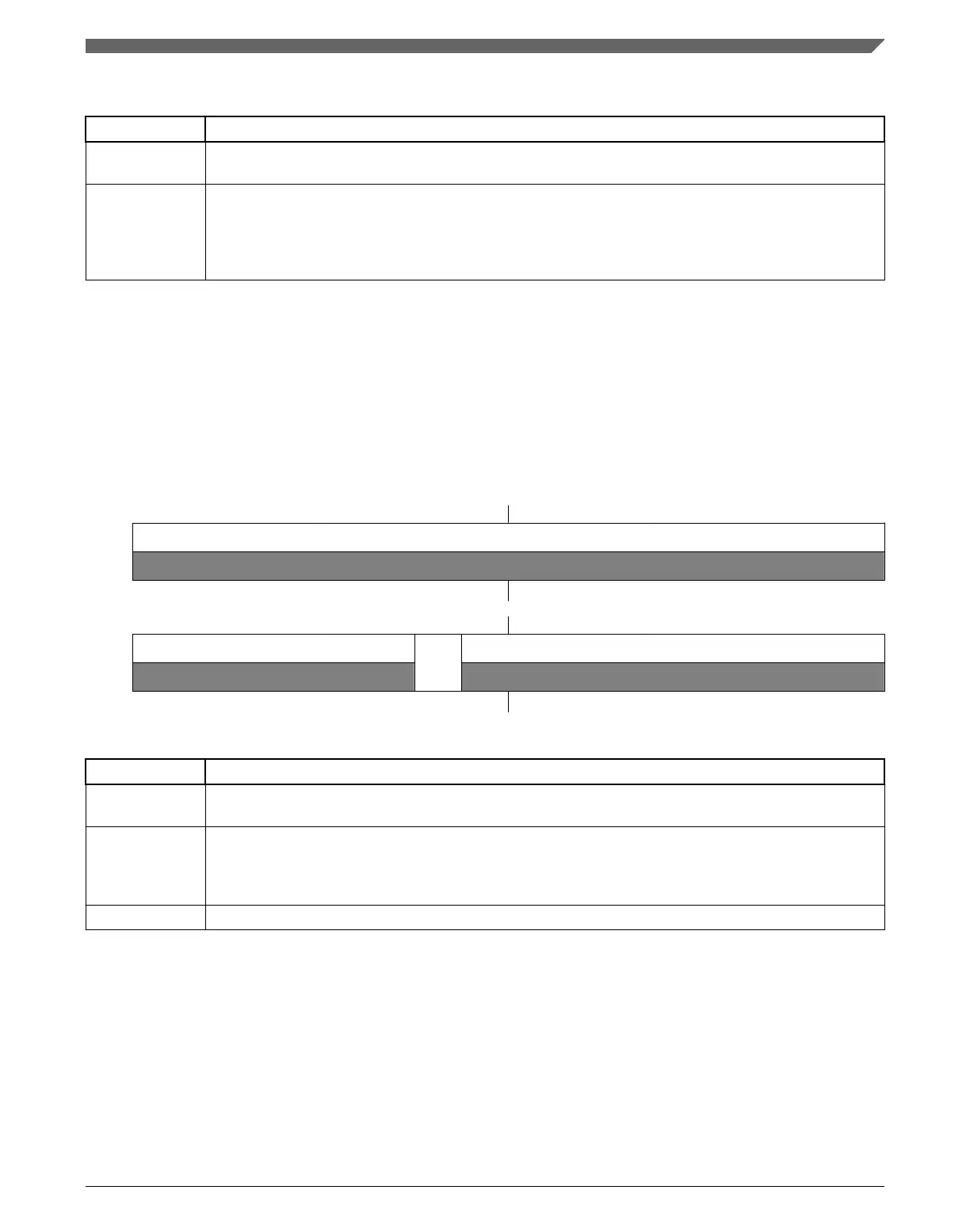

18.2.3 Crossbar Switch (AXBS) Control Register (MCM_PLACR)

The PLACR register selects the arbitration policy for the crossbar masters.

Address:

E008_0000h base + Ch offset = E008_000Ch

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

ARB

Reserved

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

MCM_PLACR field descriptions

Field Description

31–10

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

9

ARB

Arbitration select

0 Fixed-priority arbitration for the crossbar masters

1 Round-robin arbitration for the crossbar masters

Reserved This field is reserved.

18.2.4 Interrupt Status and Control Register (MCM_ISCR)

The MCM_ISCR register includes the enable and status bits associated with the core’s

floating-point exceptions. The individual event indicators are first qualified with their

exception enables and then logically summed to form an interrupt request sent to the

core’s NVIC.

Chapter 18 Miscellaneous Control Module (MCM)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 401

Loading...

Loading...