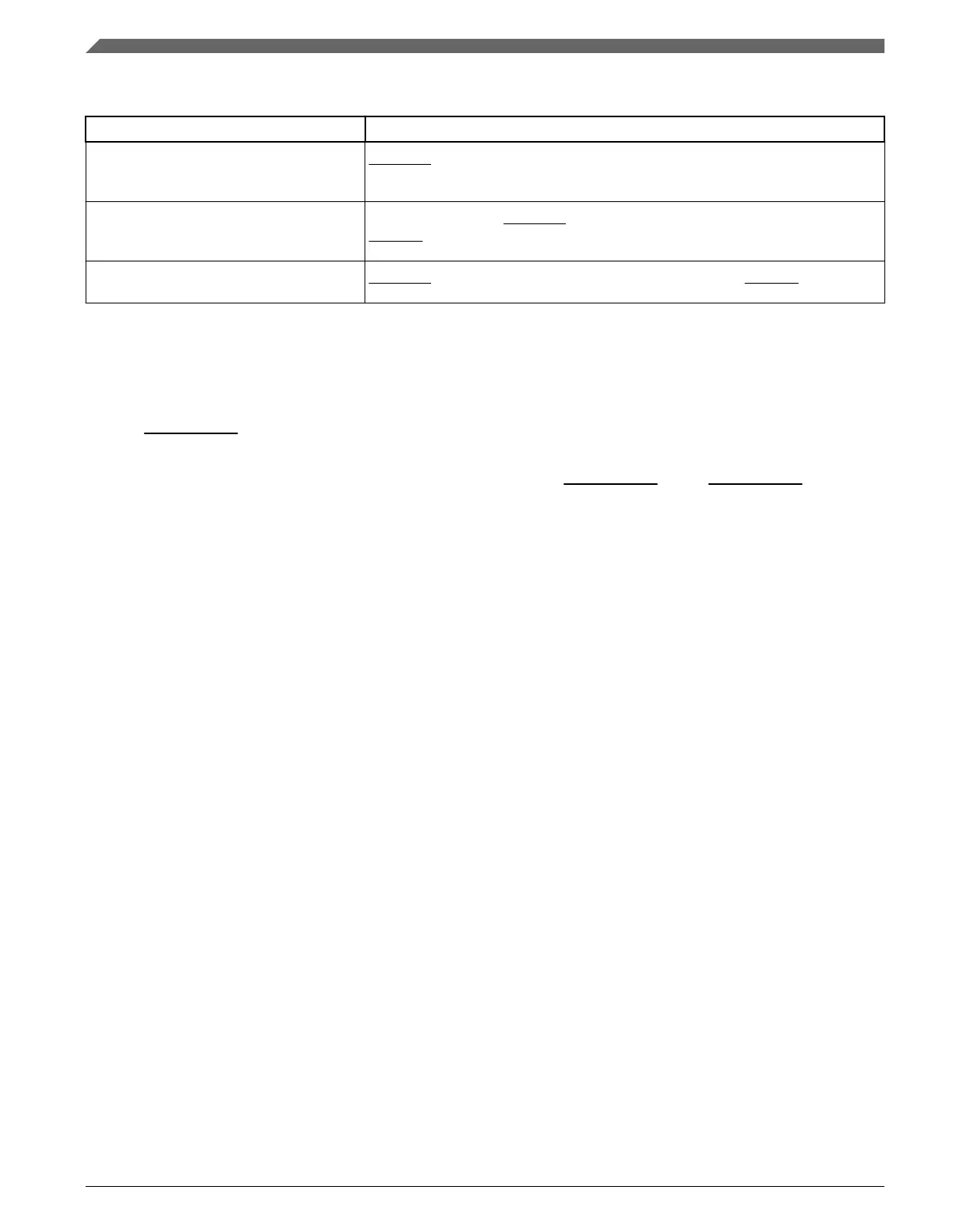

Table 23-2. EWM Refresh Mechanisms

Condition Mechanism

An EWM refresh action completes when:

CMPL < Counter < CMPH.

The software behaves as expected and the EWM counter is reset to zero. The

EWM_out output signal remains in the deasserted state if, during the EWM

refresh action, the EWM_in input has been in deasserted state..

An EWM refresh action completes when

Counter < CMPL

The software refreshes the EWM before the windowed time frame, the counter is

reset to zero and the EWM_out output signal is asserted irrespective of the input

EWM_in.

Counter value reaches CMPH prior to

completion of EWM refresh action.

Software has not refreshed the EWM. The EWM counter is reset to zero and the

EWM_out output signal is asserted irrespective of the input EWM_in.

23.4.6 EWM Interrupt

When EWM_out is asserted, an interrupt request is generated to indicate the assertion of

the EWM reset out signal. This interrupt is enabled when CTRL[INTEN] is set. Clearing

this bit clears the interrupt request but does not affect EWM_out. The EWM_out signal

can be deasserted only by forcing a system reset.

23.4.7

Counter clock prescaler

The EWM counter clock source can be prescaled by a clock divider, by programming

CLKPRESCALER[CLK_DIV]. This divided clock is used to run the EWM counter.

NOTE

The divided clock used to run the EWM counter must be no

more than half the frequency of the bus clock.

Functional Description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

518 NXP Semiconductors

Loading...

Loading...