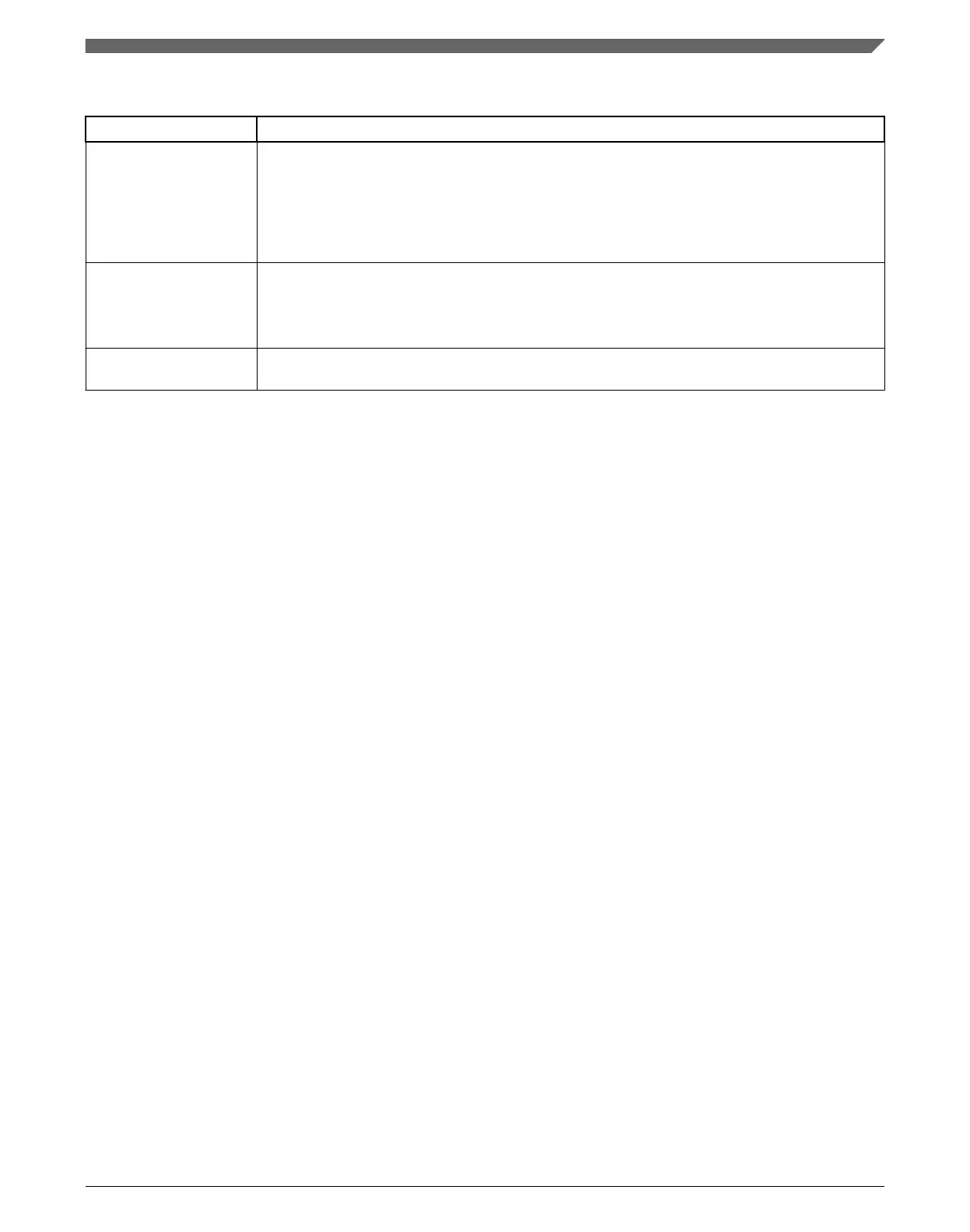

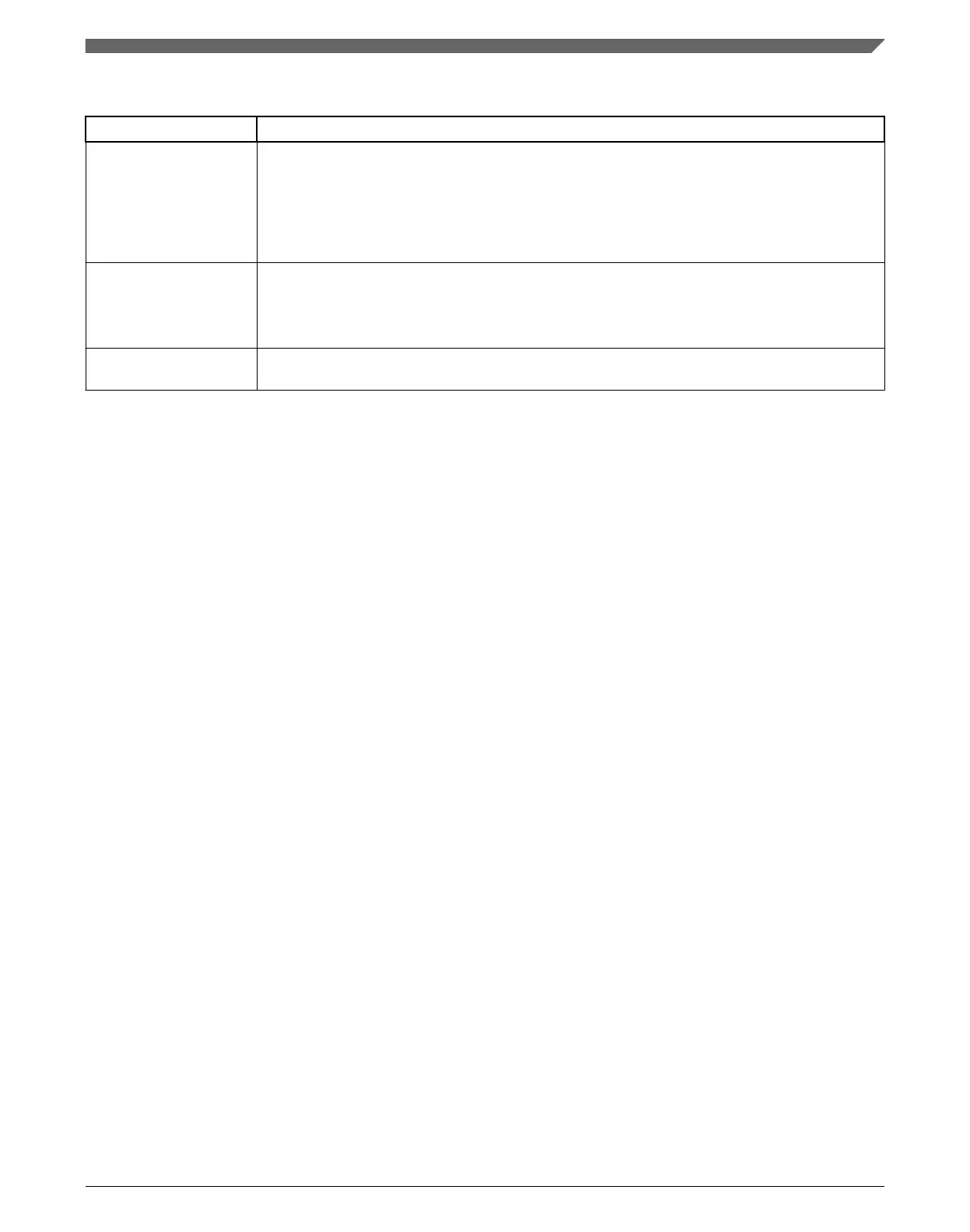

Table 22-3. Modes of operation

Mode Description

Normal In Normal mode, the eDMA transfers data between a source and a destination. The source and

destination can be a memory block or an I/O block capable of operation with the eDMA.

A service request initiates a transfer of a specific number of bytes (NBYTES) as specified in the

transfer control descriptor (TCD). The minor loop is the sequence of read-write operations that

transfers these NBYTES per service request. Each service request executes one iteration of the

major loop, which transfers NBYTES of data.

Debug DMA operation is configurable in Debug mode via the control register:

• If CR[EDBG] is cleared, the DMA continues to operate.

• If CR[EDBG] is set, the eDMA stops transferring data. If Debug mode is entered while a

channel is active, the eDMA continues operation until the channel retires.

Wait Before entering Wait mode, the DMA attempts to complete its current transfer. After the transfer

completes, the device enters Wait mode.

22.3 Memory map/register definition

The eDMA's programming model is partitioned into two regions:

• The first region defines a number of registers providing control functions

• The second region corresponds to the local transfer control descriptor (TCD)

memory

22.3.1

TCD memory

Each channel requires a 32-byte transfer control descriptor for defining the desired data

movement operation. The channel descriptors are stored in the local memory in

sequential order: channel 0, channel 1, ... channel 15. Each TCDn definition is presented

as 11 registers of 16 or 32 bits.

22.3.2

TCD initialization

Prior to activating a channel, you must initialize its TCD with the appropriate transfer

profile.

Chapter 22 Enhanced Direct Memory Access (eDMA)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 429

Loading...

Loading...