MCG_C8 field descriptions (continued)

Field Description

clock indication. The CME1 bit should be set to a logic 1 when the MCG is in an operational mode that

uses the RTC as its external reference clock or if the RTC is operational. CME1 bit must be set to a logic 0

before the MCG enters any Stop mode. Otherwise, a reset request may occur when in Stop mode. CME1

should also be set to a logic 0 before entering VLPR or VLPW power modes.

0 External clock monitor is disabled for RTC clock.

1 External clock monitor is enabled for RTC clock.

4–1

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

0

LOCS1

RTC Loss of Clock Status

This bit indicates when a loss of clock has occurred. This bit is cleared by writing a logic 1 to it when set.

0 Loss of RTC has not occur.

1 Loss of RTC has occur

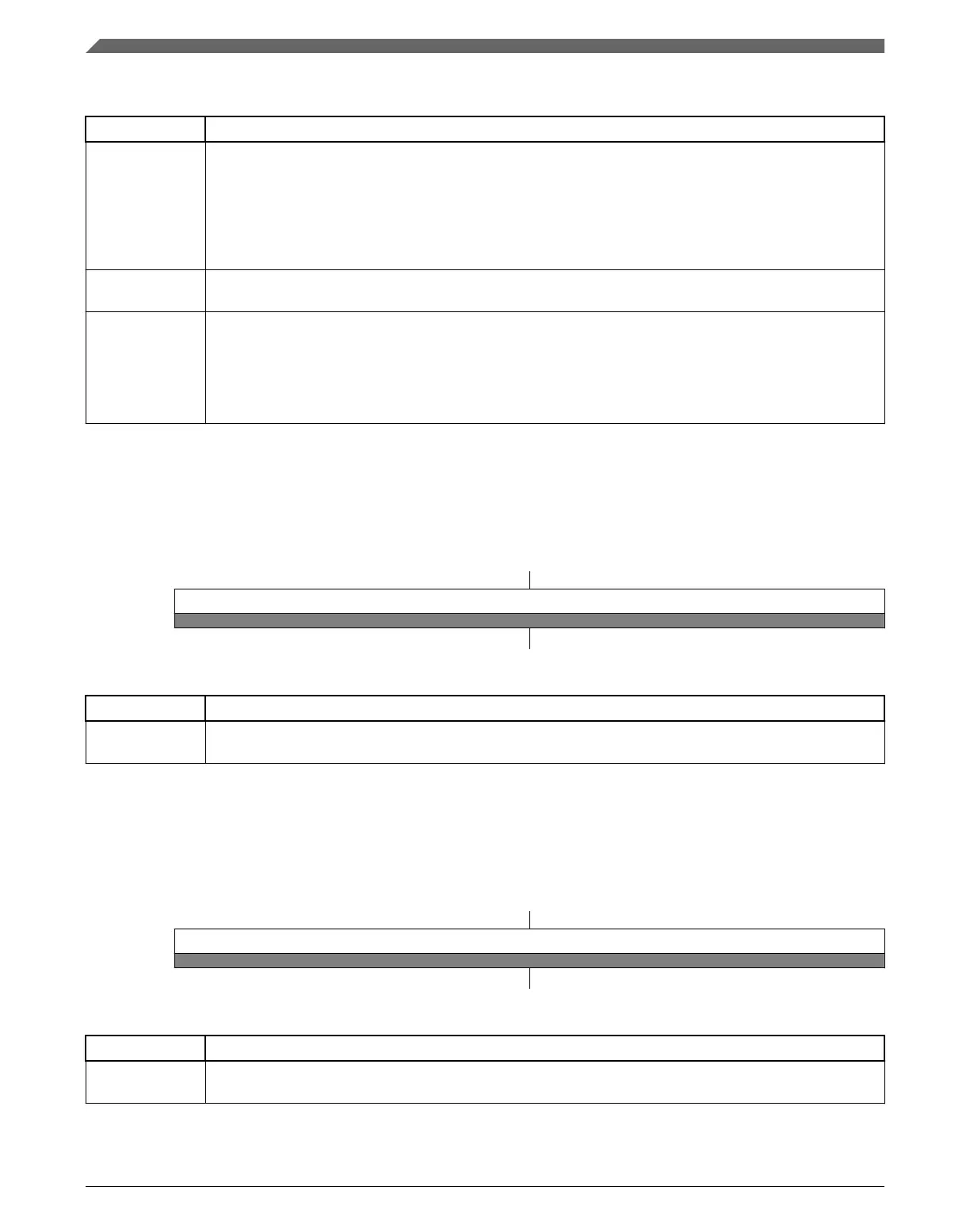

25.3.13 MCG Control 12 Register (MCG_C12)

Address: 4006_4000h base + 11h offset = 4006_4011h

Bit 7 6 5 4 3 2 1 0

Read 0

Write

Reset

0 0 0 0 0 0 0 0

MCG_C12 field descriptions

Field Description

Reserved This field is reserved.

This read-only field is reserved and always has the value 0.

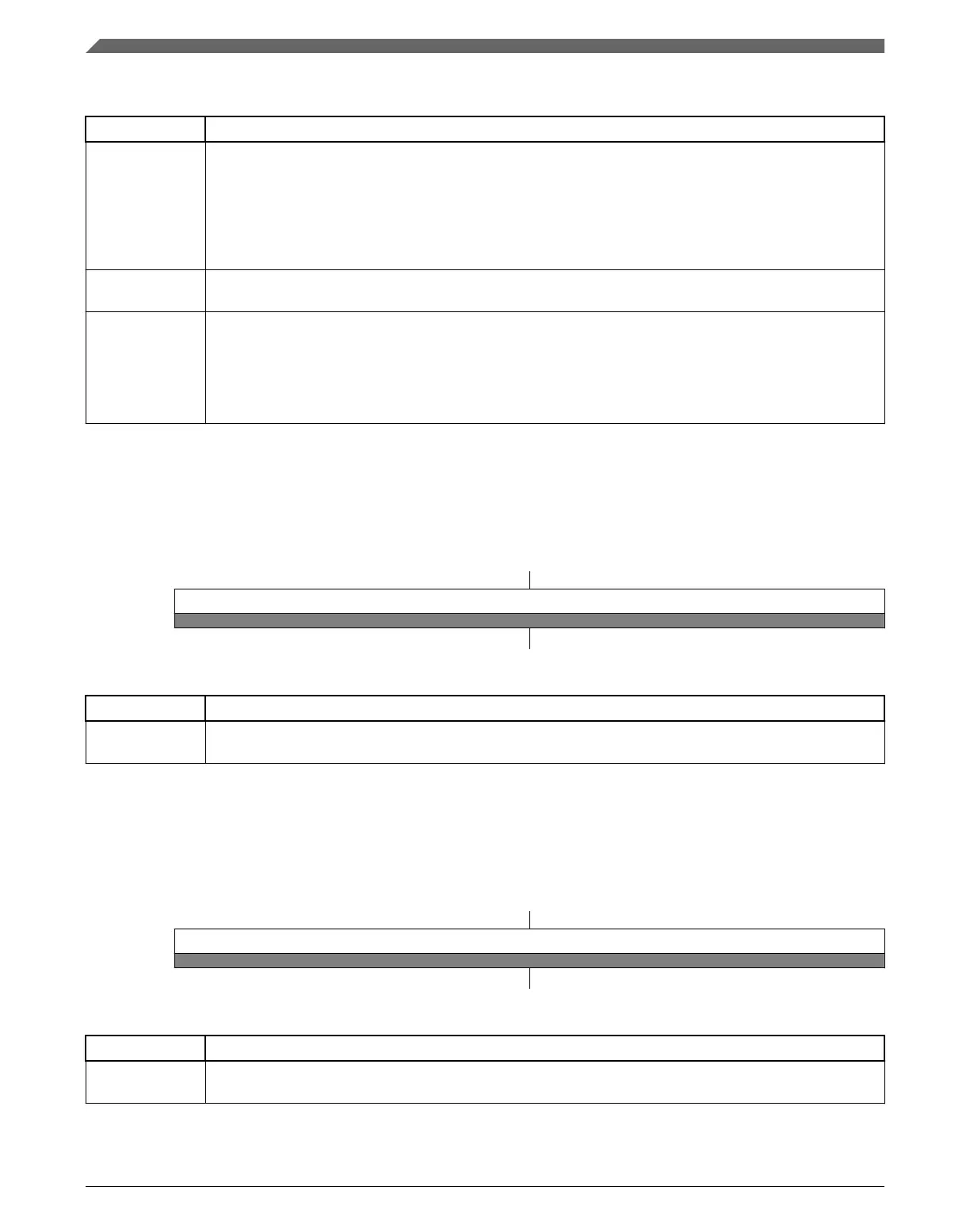

25.3.13 MCG Status 2 Register (MCG_S2)

Address: 4006_4000h base + 12h offset = 4006_4012h

Bit 7 6 5 4 3 2 1 0

Read 0

Write

Reset

0 0 0 0 0 0 0 0

MCG_S2 field descriptions

Field Description

Reserved This field is reserved.

This read-only field is reserved and always has the value 0.

Memory Map/Register Definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

556 NXP Semiconductors

Loading...

Loading...