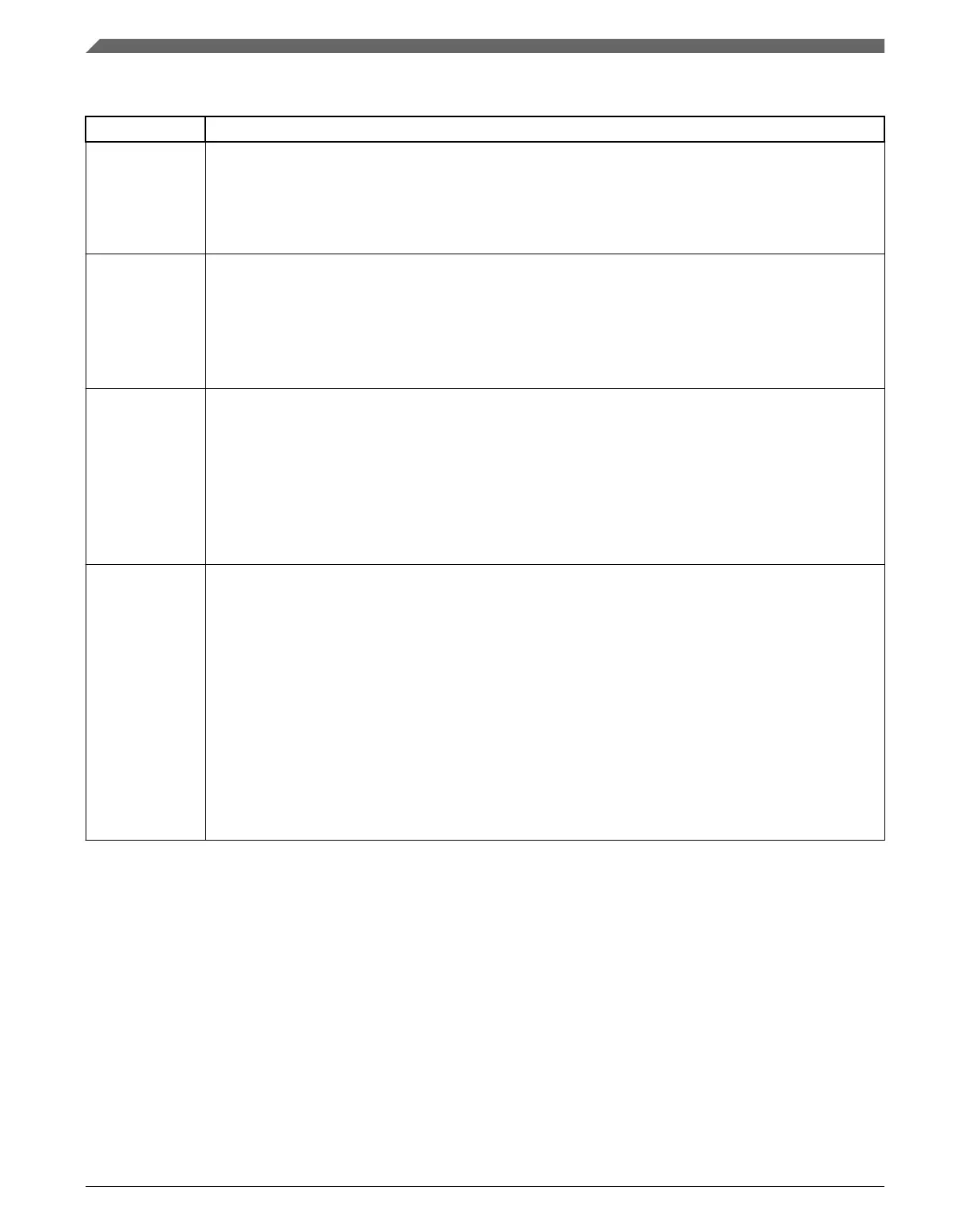

FTMx_SC field descriptions (continued)

Field Description

6

TOIE

Timer Overflow Interrupt Enable

Enables FTM overflow interrupts.

0 Disable TOF interrupts. Use software polling.

1 Enable TOF interrupts. An interrupt is generated when TOF equals one.

5

CPWMS

Center-Aligned PWM Select

Selects CPWM mode. This mode configures the FTM to operate in Up-Down Counting mode.

This field is write protected. It can be written only when MODE[WPDIS] = 1.

0 FTM counter operates in Up Counting mode.

1 FTM counter operates in Up-Down Counting mode.

4–3

CLKS

Clock Source Selection

Selects FTM counter clock sources.

This field is write protected. It can be written only when MODE[WPDIS] = 1.

00 No clock selected. This in effect disables the FTM counter.

01 System clock

10 Fixed frequency clock

11 External clock

PS Prescale Factor Selection

Selects one of 8 division factors for the clock source selected by CLKS. The new prescaler factor affects

the clock source on the next system clock cycle after the new value is updated into the register bits.

This field is write protected. It can be written only when MODE[WPDIS] = 1.

000 Divide by 1

001 Divide by 2

010 Divide by 4

011 Divide by 8

100 Divide by 16

101 Divide by 32

110 Divide by 64

111 Divide by 128

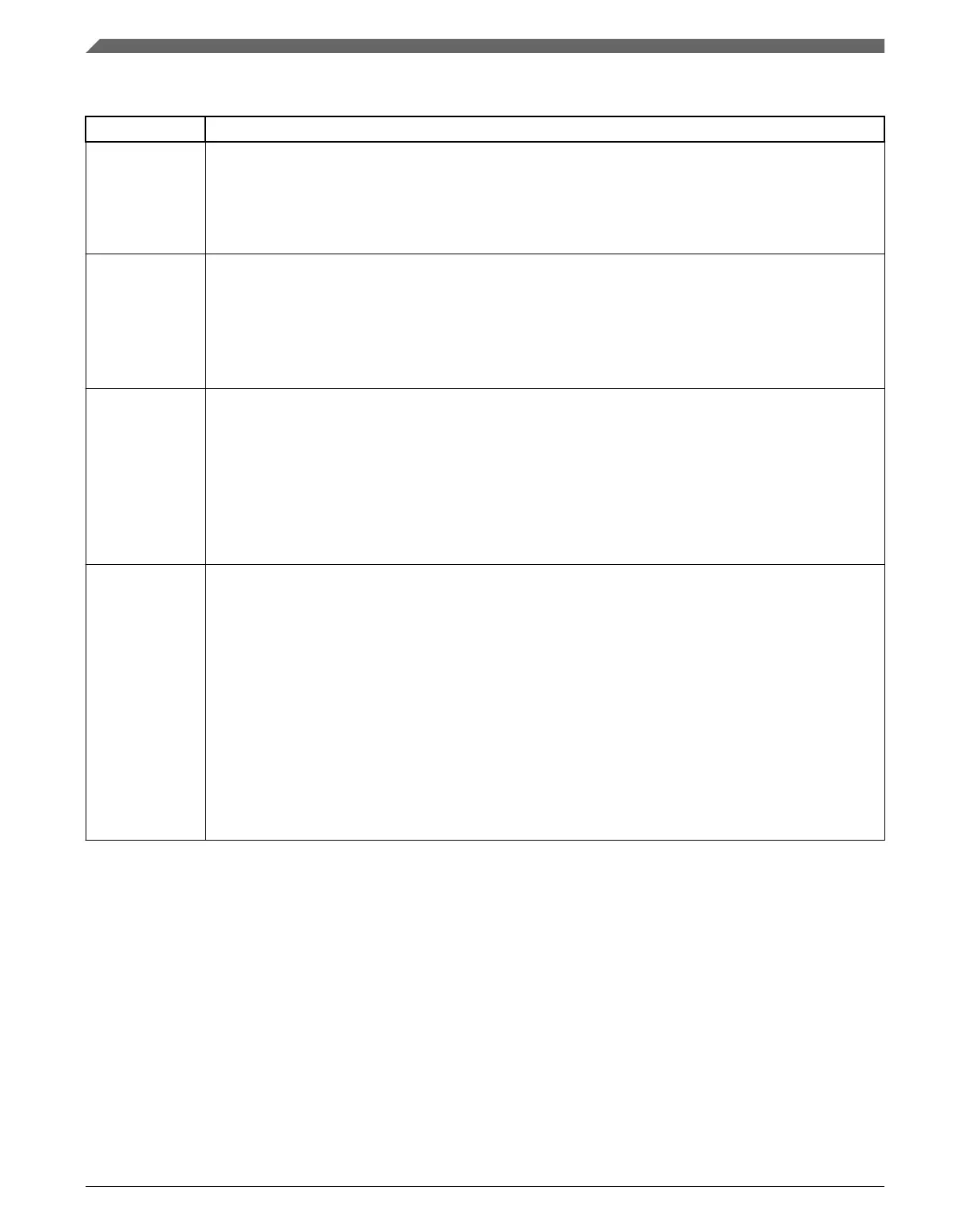

39.3.4 Counter (FTMx_CNT)

The CNT register contains the FTM counter value.

Reset clears the CNT register. Writing any value to COUNT updates the counter with its

initial value, CNTIN.

When BDM is active, the FTM counter is frozen. This is the value that you may read.

Memory map and register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

904 NXP Semiconductors

Loading...

Loading...