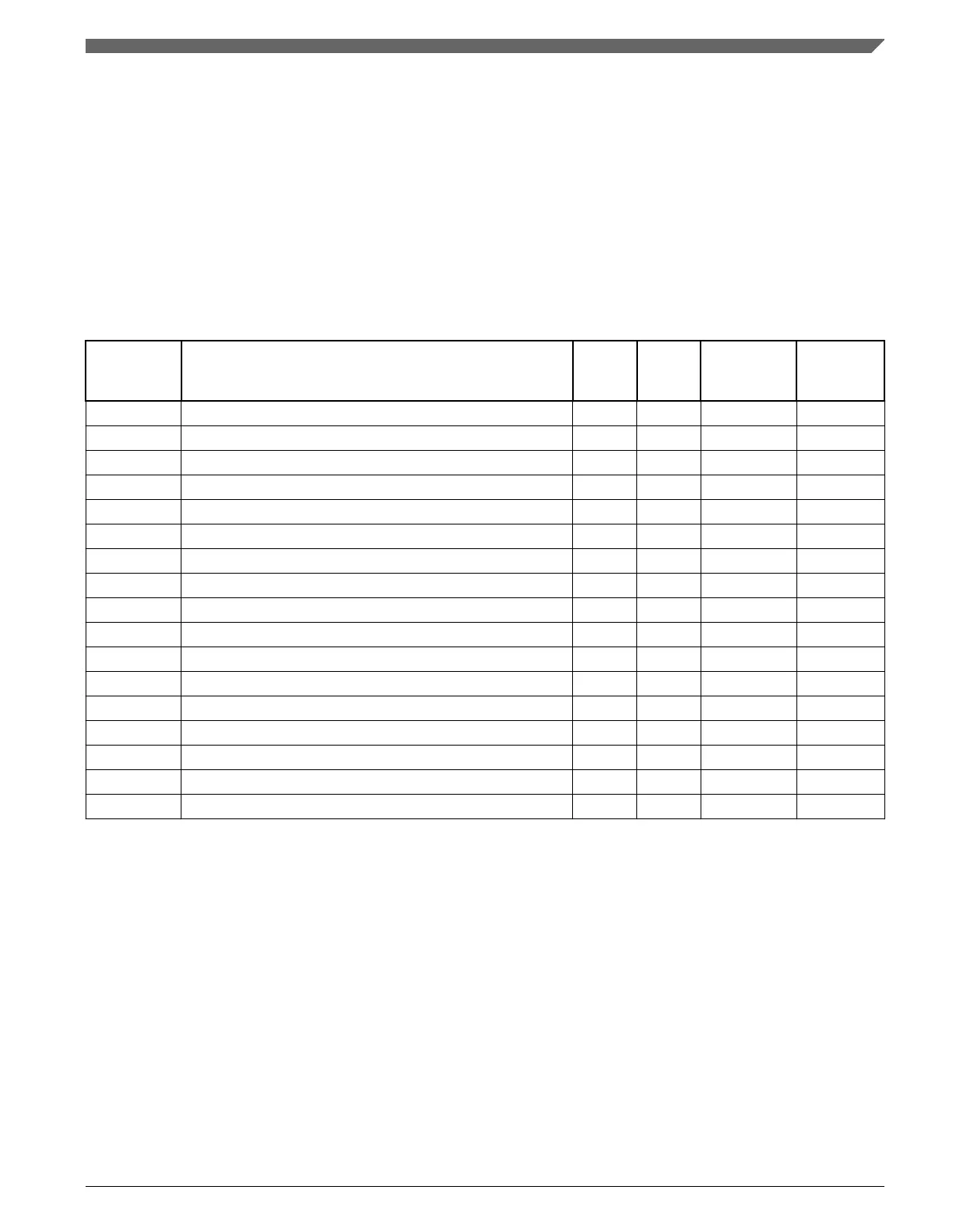

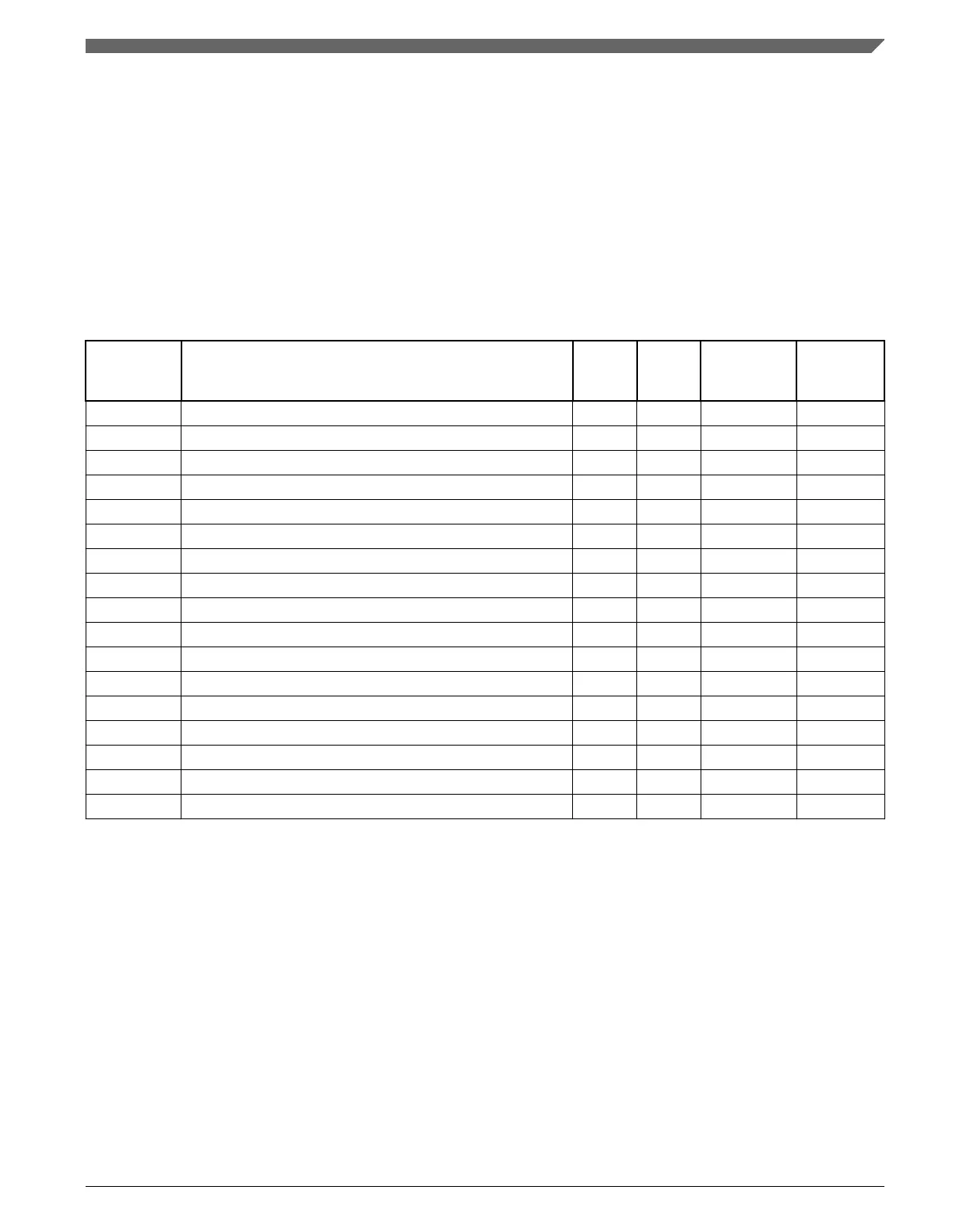

40.3 Memory map/register description

This section provides a detailed description of all registers accessible in the PIT module.

• Reserved registers will read as 0, writes will have no effect.

• See the chip-specific PIT information for the number of PIT channels used in this

MCU.

PIT memory map

Absolute

address

(hex)

Register name

Width

(in bits)

Access Reset value

Section/

page

4003_7000 PIT Module Control Register (PIT_MCR) 32 R/W 0000_0006h 40.3.1/1031

4003_7100 Timer Load Value Register (PIT_LDVAL0) 32 R/W 0000_0000h 40.3.2/1033

4003_7104 Current Timer Value Register (PIT_CVAL0) 32 R 0000_0000h 40.3.3/1033

4003_7108 Timer Control Register (PIT_TCTRL0) 32 R/W 0000_0000h 40.3.4/1034

4003_710C Timer Flag Register (PIT_TFLG0) 32 R/W 0000_0000h 40.3.5/1034

4003_7110 Timer Load Value Register (PIT_LDVAL1) 32 R/W 0000_0000h 40.3.2/1033

4003_7114 Current Timer Value Register (PIT_CVAL1) 32 R 0000_0000h 40.3.3/1033

4003_7118 Timer Control Register (PIT_TCTRL1) 32 R/W 0000_0000h 40.3.4/1034

4003_711C Timer Flag Register (PIT_TFLG1) 32 R/W 0000_0000h 40.3.5/1034

4003_7120 Timer Load Value Register (PIT_LDVAL2) 32 R/W 0000_0000h 40.3.2/1033

4003_7124 Current Timer Value Register (PIT_CVAL2) 32 R 0000_0000h 40.3.3/1033

4003_7128 Timer Control Register (PIT_TCTRL2) 32 R/W 0000_0000h 40.3.4/1034

4003_712C Timer Flag Register (PIT_TFLG2) 32 R/W 0000_0000h 40.3.5/1034

4003_7130 Timer Load Value Register (PIT_LDVAL3) 32 R/W 0000_0000h 40.3.2/1033

4003_7134 Current Timer Value Register (PIT_CVAL3) 32 R 0000_0000h 40.3.3/1033

4003_7138 Timer Control Register (PIT_TCTRL3) 32 R/W 0000_0000h 40.3.4/1034

4003_713C Timer Flag Register (PIT_TFLG3) 32 R/W 0000_0000h 40.3.5/1034

40.3.1 PIT Module Control Register (PIT_MCR)

This register enables or disables the PIT timer clocks and controls the timers when the

PIT enters the Debug mode.

Access: User read/write

Chapter 40 Periodic Interrupt Timer (PIT)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1031

Loading...

Loading...