DMA_CR field descriptions (continued)

Field Description

4

HOE

Halt On Error

0 Normal operation

1 Any error causes the HALT bit to set. Subsequently, all service requests are ignored until the HALT bit

is cleared.

3

Reserved

This field is reserved.

Reserved

2

ERCA

Enable Round Robin Channel Arbitration

0 Fixed priority arbitration is used for channel selection .

1 Round robin arbitration is used for channel selection .

1

EDBG

Enable Debug

0 When in debug mode, the DMA continues to operate.

1 When in debug mode, the DMA stalls the start of a new channel. Executing channels are allowed to

complete. Channel execution resumes when the system exits debug mode or the EDBG bit is cleared.

0

Reserved

This field is reserved.

Reserved

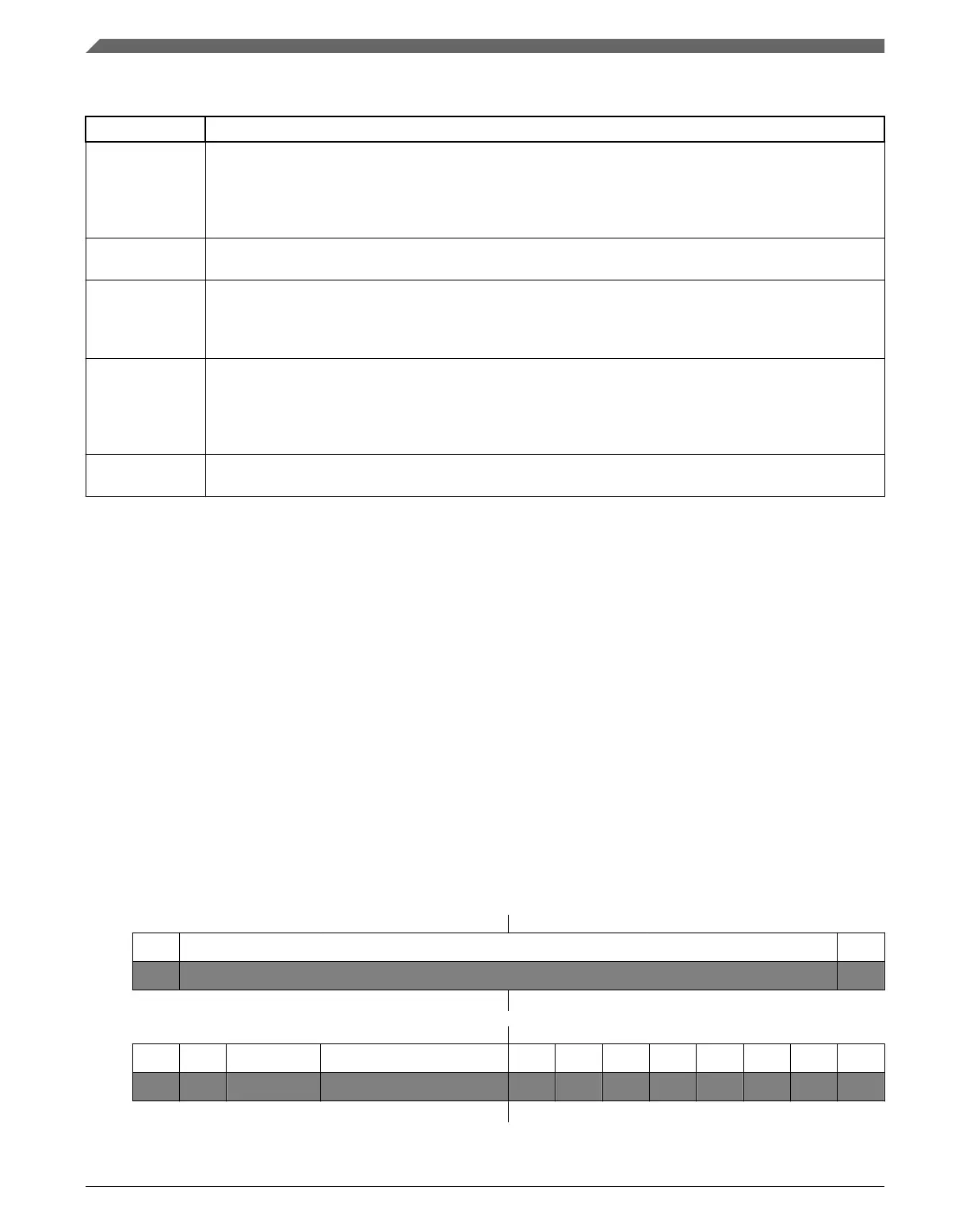

22.3.6 Error Status Register (DMA_ES)

The ES provides information concerning the last recorded channel error. Channel errors

can be caused by:

• A configuration error, that is:

• An illegal setting in the transfer-control descriptor, or

• An illegal priority register setting in fixed-arbitration

• An error termination to a bus master read or write cycle

• A cancel transfer with error bit that will be set when a transfer is canceled via the

corresponding cancel transfer control bit

See Fault reporting and handling for more details.

Address:

4000_8000h base + 4h offset = 4000_8004h

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

VLD 0 ECX

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0 CPE 0 ERRCHN SAE SOE DAE DOE NCE SGE SBE DBE

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Memory map/register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

444 NXP Semiconductors

Loading...

Loading...