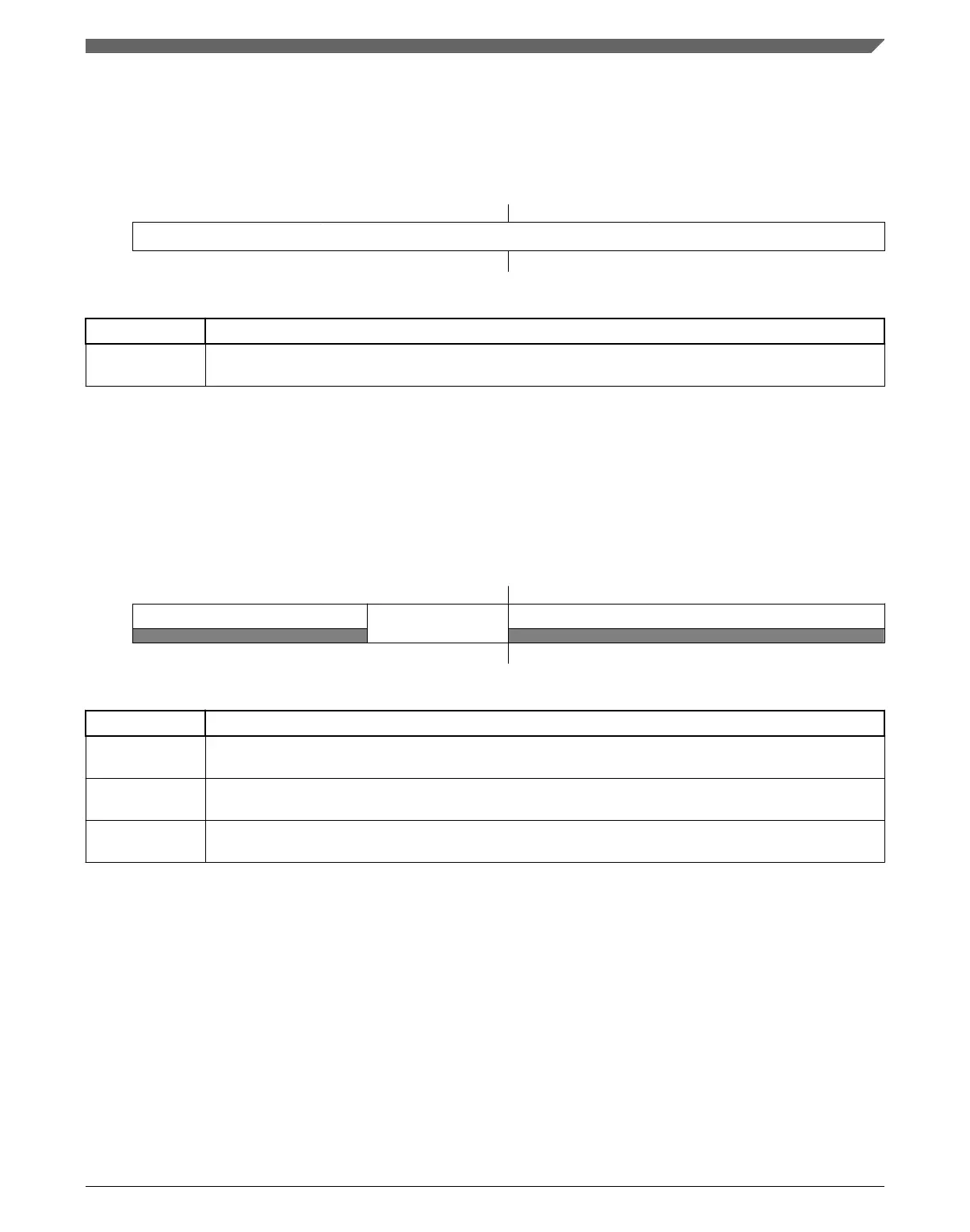

24.7.11 Watchdog Reset Count register (WDOG_RSTCNT)

Address: 4005_2000h base + 14h offset = 4005_2014h

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Read

RSTCNT

Write

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

WDOG_RSTCNT field descriptions

Field Description

RSTCNT Counts the number of times the watchdog resets the system. This register is reset only on a POR. Writing

1 to the bit to be cleared enables you to clear the contents of this register.

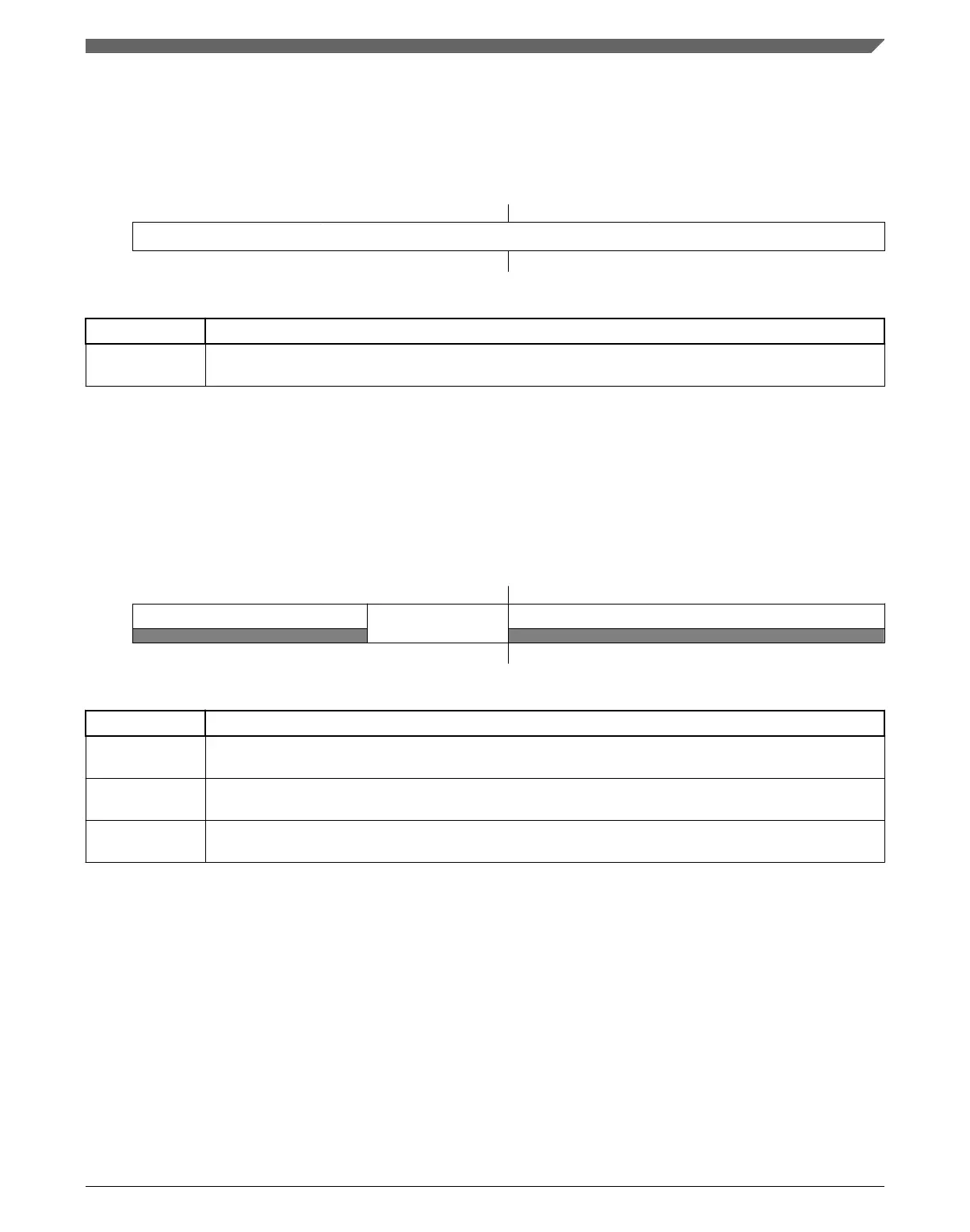

24.7.12 Watchdog Prescaler register (WDOG_PRESC)

Address: 4005_2000h base + 16h offset = 4005_2016h

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Read 0

PRESCVAL

0

Write

Reset

0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0

WDOG_PRESC field descriptions

Field Description

15–11

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

10–8

PRESCVAL

3-bit prescaler for the watchdog clock source. A value of zero indicates no division of the input WDOG

clock. The watchdog clock is divided by (PRESCVAL + 1) to provide the prescaled WDOG_CLK.

Reserved This field is reserved.

This read-only field is reserved and always has the value 0.

24.8 Watchdog operation with 8-bit access

24.8.1 General guideline

When performing 8-bit accesses to the watchdog's 16-bit registers where the intention is

to access both the bytes of a register, place the two 8-bit accesses one after the other in

your code.

Chapter 24 Watchdog Timer (WDOG)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 535

Loading...

Loading...