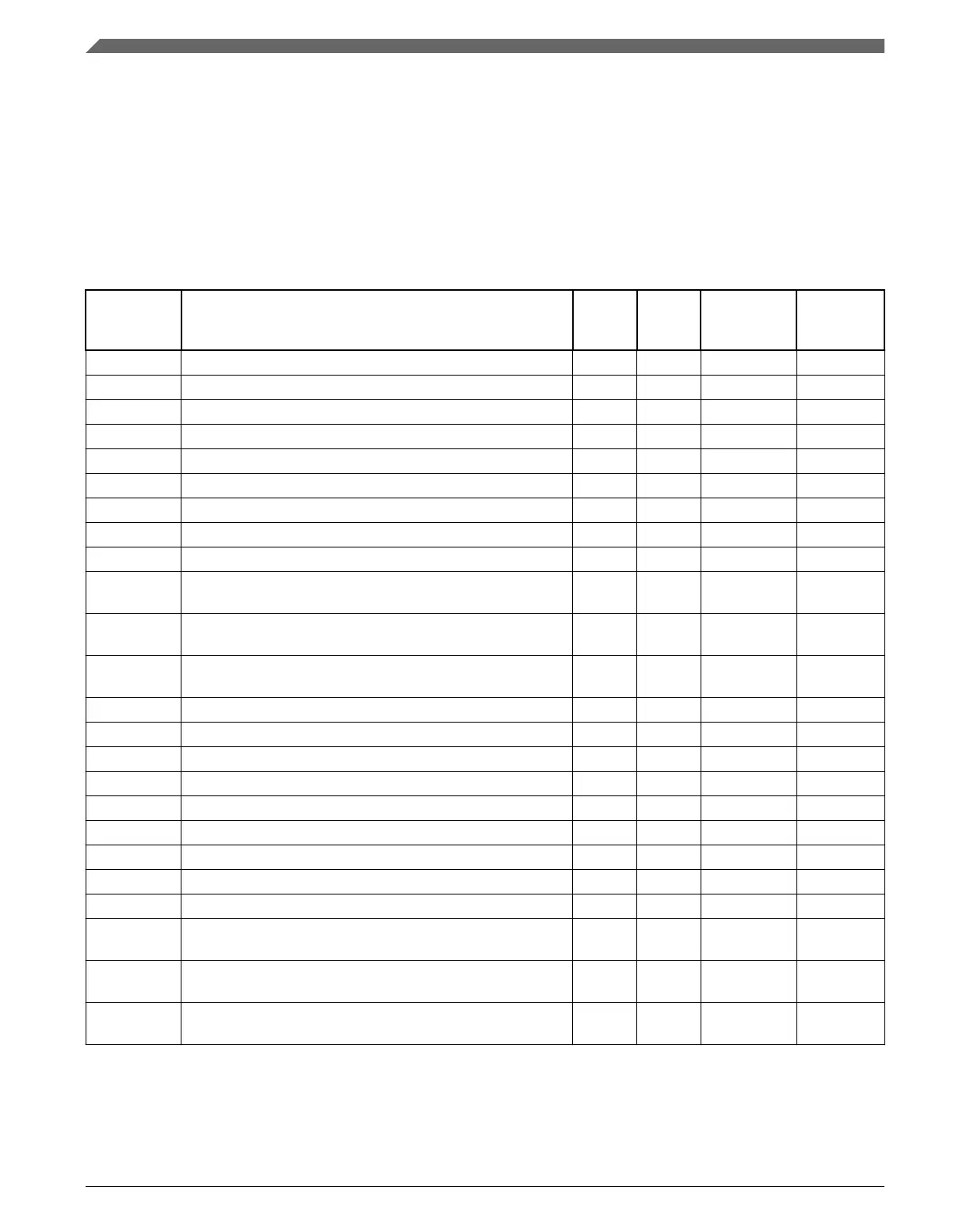

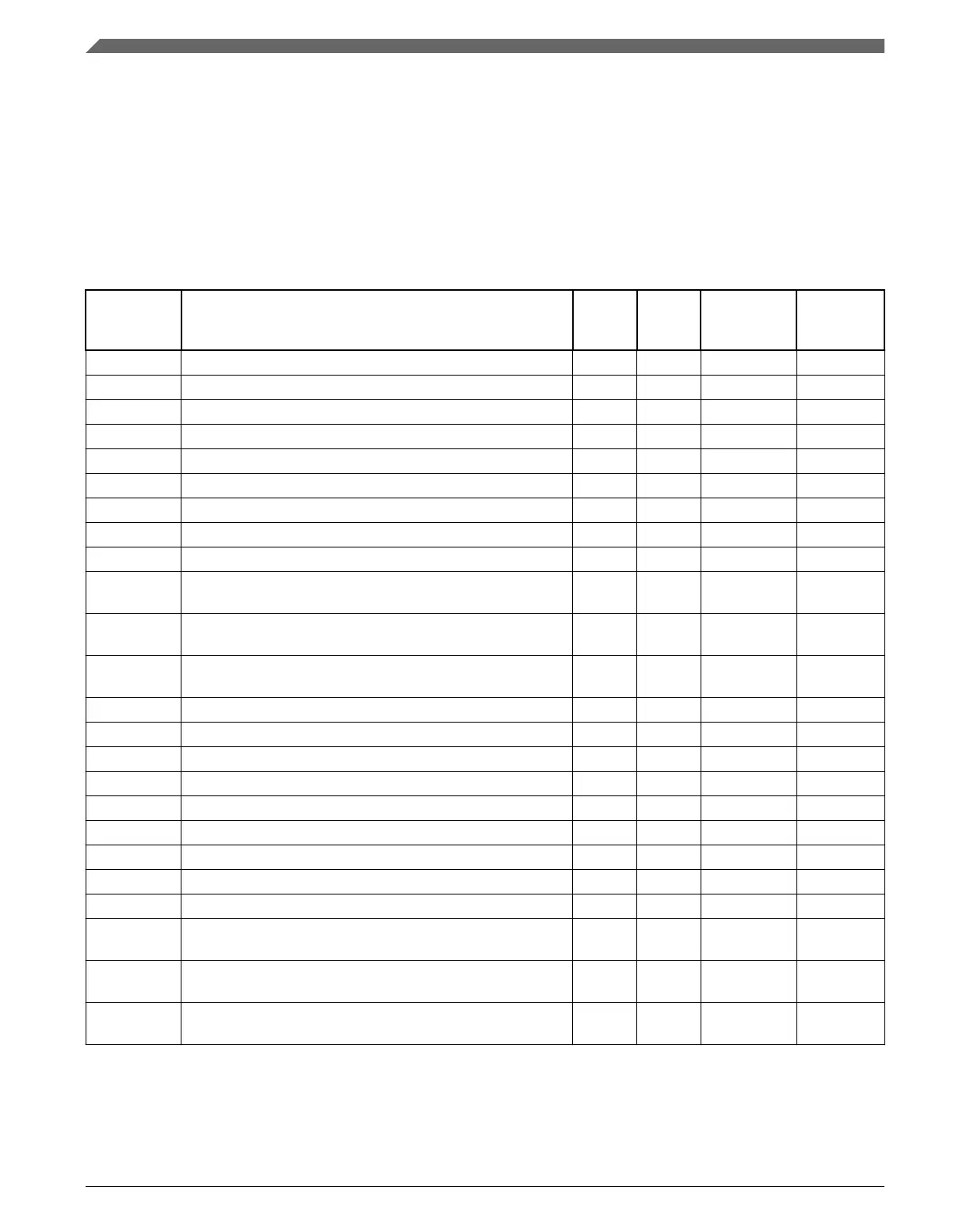

46.3 Memory map/register definition

This section describes in detail all I2C registers accessible to the end user.

I2C memory map

Absolute

address

(hex)

Register name

Width

(in bits)

Access Reset value

Section/

page

4006_6000 I2C Address Register 1 (I2C0_A1) 8 R/W 00h 46.3.1/1185

4006_6001 I2C Frequency Divider register (I2C0_F) 8 R/W 00h 46.3.2/1185

4006_6002 I2C Control Register 1 (I2C0_C1) 8 R/W 00h 46.3.3/1186

4006_6003 I2C Status register (I2C0_S) 8 R/W 80h 46.3.4/1188

4006_6004 I2C Data I/O register (I2C0_D) 8 R/W 00h 46.3.5/1190

4006_6005 I2C Control Register 2 (I2C0_C2) 8 R/W 00h 46.3.6/1190

4006_6006 I2C Programmable Input Glitch Filter Register (I2C0_FLT) 8 R/W 00h 46.3.7/1191

4006_6007 I2C Range Address register (I2C0_RA) 8 R/W 00h 46.3.8/1193

4006_6008 I2C SMBus Control and Status register (I2C0_SMB) 8 R/W 00h 46.3.9/1193

4006_6009 I2C Address Register 2 (I2C0_A2) 8 R/W C2h

46.3.10/

1195

4006_600A I2C SCL Low Timeout Register High (I2C0_SLTH) 8 R/W 00h

46.3.11/

1195

4006_600B I2C SCL Low Timeout Register Low (I2C0_SLTL) 8 R/W 00h

46.3.12/

1196

4006_7000 I2C Address Register 1 (I2C1_A1) 8 R/W 00h 46.3.1/1185

4006_7001 I2C Frequency Divider register (I2C1_F) 8 R/W 00h 46.3.2/1185

4006_7002 I2C Control Register 1 (I2C1_C1) 8 R/W 00h 46.3.3/1186

4006_7003 I2C Status register (I2C1_S) 8 R/W 80h 46.3.4/1188

4006_7004 I2C Data I/O register (I2C1_D) 8 R/W 00h 46.3.5/1190

4006_7005 I2C Control Register 2 (I2C1_C2) 8 R/W 00h 46.3.6/1190

4006_7006 I2C Programmable Input Glitch Filter Register (I2C1_FLT) 8 R/W 00h 46.3.7/1191

4006_7007 I2C Range Address register (I2C1_RA) 8 R/W 00h 46.3.8/1193

4006_7008 I2C SMBus Control and Status register (I2C1_SMB) 8 R/W 00h 46.3.9/1193

4006_7009 I2C Address Register 2 (I2C1_A2) 8 R/W C2h

46.3.10/

1195

4006_700A I2C SCL Low Timeout Register High (I2C1_SLTH) 8 R/W 00h

46.3.11/

1195

4006_700B I2C SCL Low Timeout Register Low (I2C1_SLTL) 8 R/W 00h

46.3.12/

1196

Memory map/register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1184 NXP Semiconductors

Loading...

Loading...