CMPx_CR1 field descriptions (continued)

Field Description

0 Analog Comparator is disabled.

1 Analog Comparator is enabled.

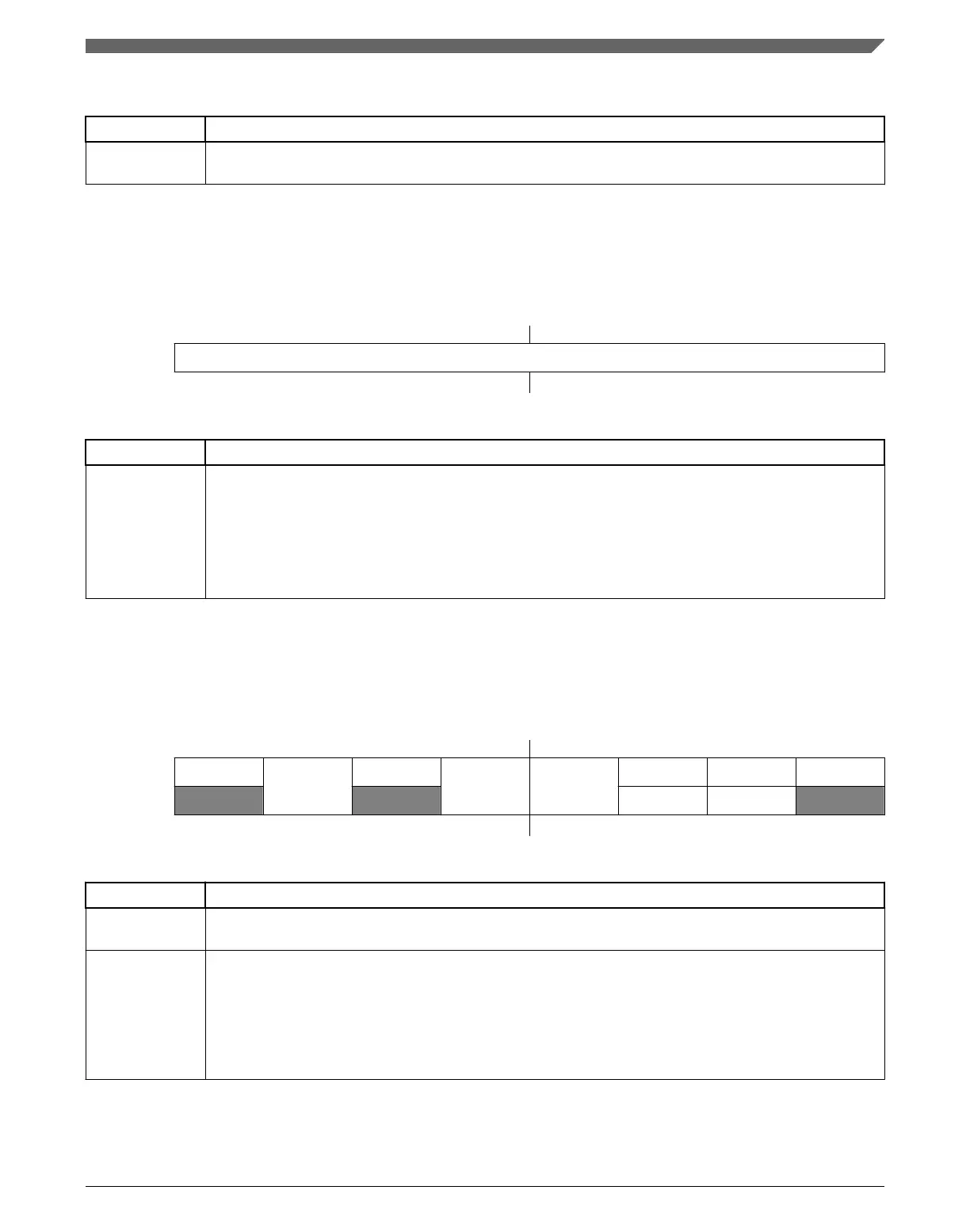

35.2.3 CMP Filter Period Register (CMPx_FPR)

Address: Base address + 2h offset

Bit 7 6 5 4 3 2 1 0

Read

FILT_PER

Write

Reset

0 0 0 0 0 0 0 0

CMPx_FPR field descriptions

Field Description

FILT_PER Filter Sample Period

Specifies the sampling period, in bus clock cycles, of the comparator output filter, when CR1[SE]=0.

Setting FILT_PER to 0x0 disables the filter. Filter programming and latency details appear in the

Functional description.

This field has no effect when CR1[SE]=1. In that case, the external SAMPLE signal is used to determine

the sampling period.

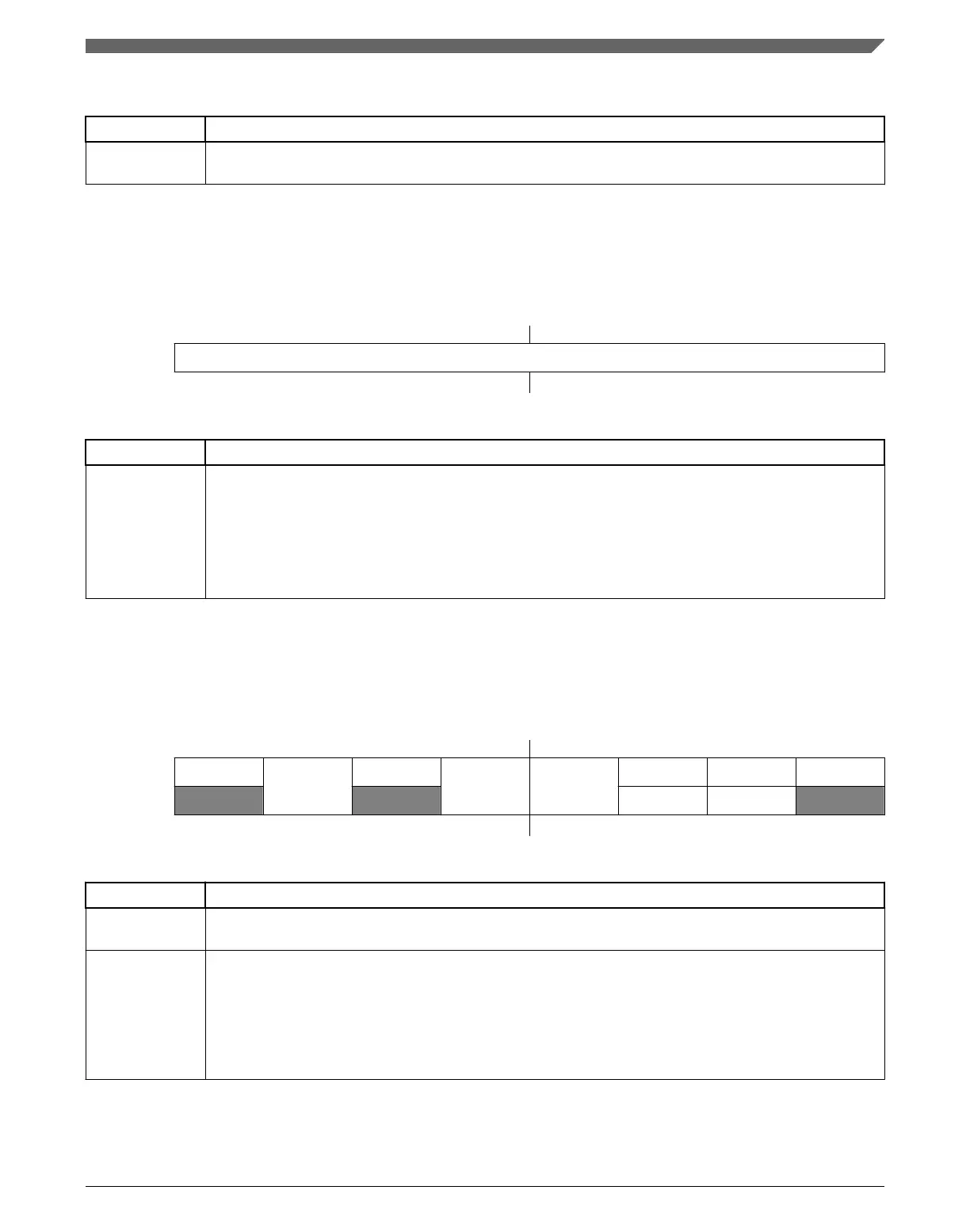

35.2.4 CMP Status and Control Register (CMPx_SCR)

Address: Base address + 3h offset

Bit 7 6 5 4 3 2 1 0

Read 0

DMAEN

0

IER IEF

CFR CFF COUT

Write w1c w1c

Reset

0 0 0 0 0 0 0 0

CMPx_SCR field descriptions

Field Description

7

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

6

DMAEN

DMA Enable Control

Enables the DMA transfer triggered from the CMP module. When this field is set, a DMA request is

asserted when CFR or CFF is set.

0 DMA is disabled.

1 DMA is enabled.

Table continues on the next page...

Chapter 35 Comparator (CMP)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 825

Loading...

Loading...