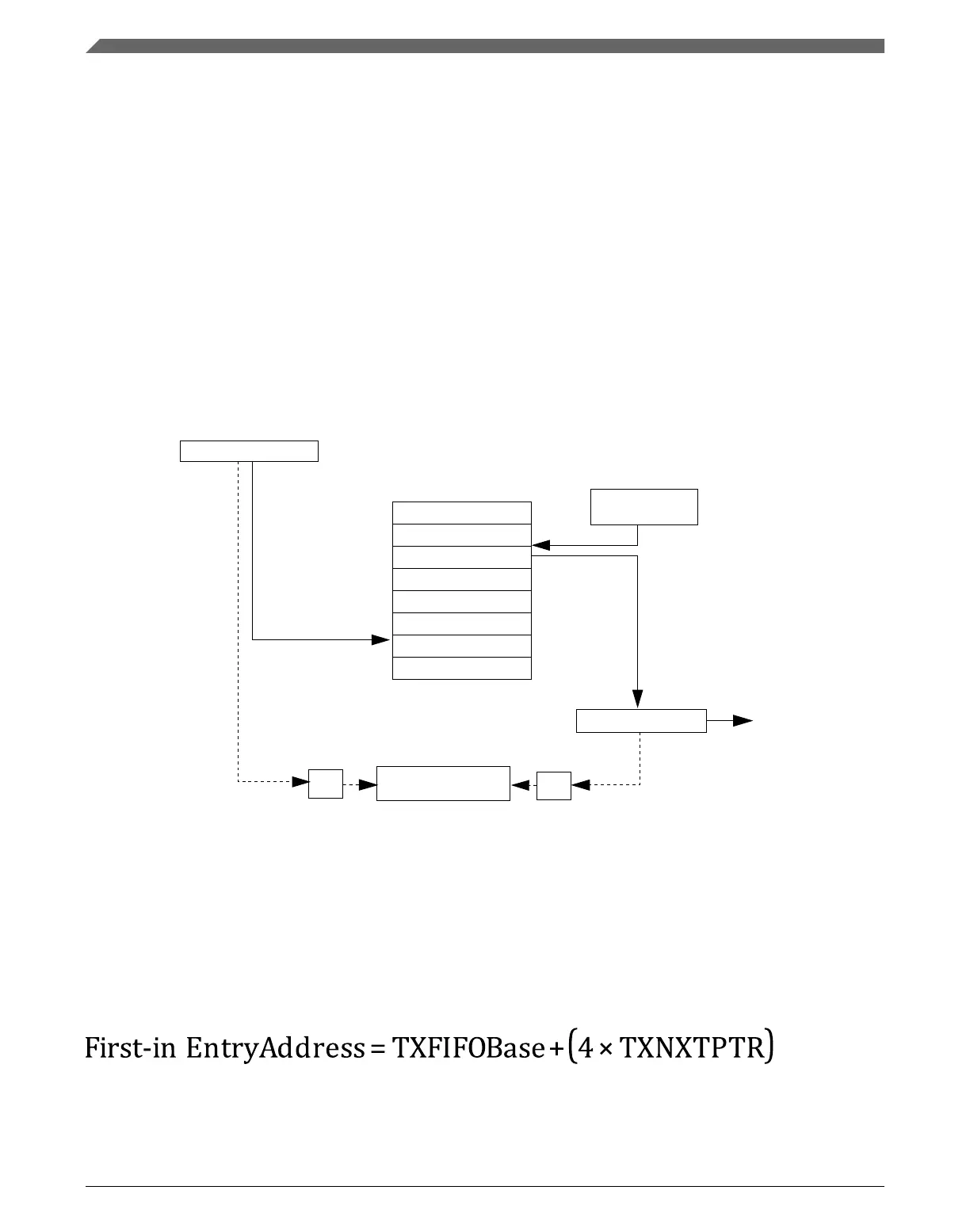

45.5.6 Calculation of FIFO pointer addresses

Complete visibility of the FIFO contents is available through the FIFO registers, and

valid entries can be identified through a memory-mapped pointer and counter for each

FIFO. The pointer to the first-in entry in each FIFO is memory mapped. For the TX FIFO

the first-in pointer is the Transmit Next Pointer (TXNXTPTR). For the RX FIFO the

first-in pointer is the Pop Next Pointer (POPNXTPTR). The following figure illustrates

the concept of first-in and last-in FIFO entries along with the FIFO Counter. The TX

FIFO is chosen for the illustration, but the concepts carry over. See Transmit First In First

Out (TX FIFO) buffering mechanism and Receive First In First Out (RX FIFO) buffering

mechanism for details on the FIFO operation.

Push TX FIFO Register

Transmit Next

Data Pointer

Shift Register

SOUT

+1

-1

TX FIFO Counter

TX FIFO Base

-

Entry C

Entry A (first in)

Entry D (last in)

Entry B

-

-

-

Figure 45-18. TX FIFO pointers and counter

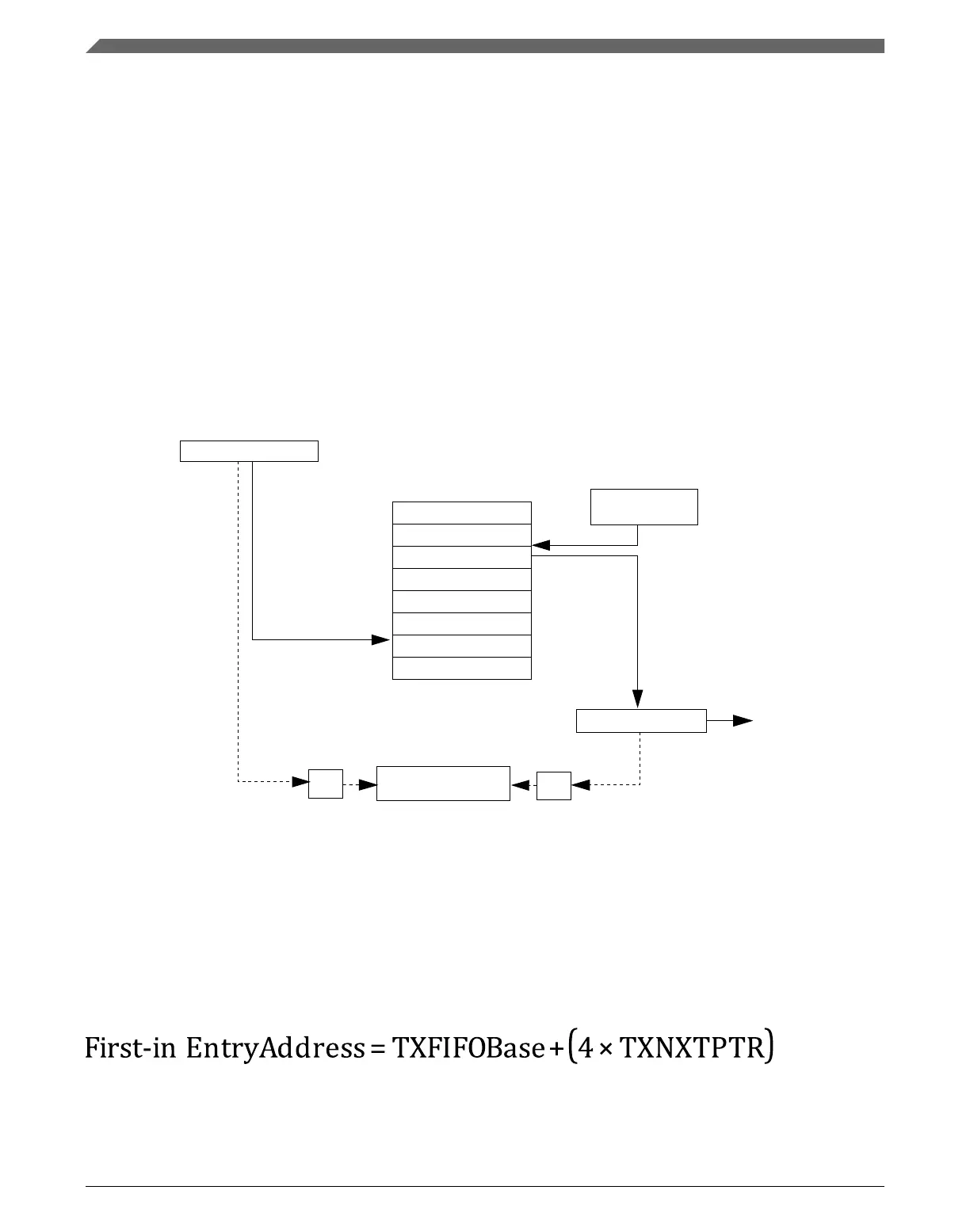

45.5.6.1

Address Calculation for the First-in Entry and Last-in Entry

in the TX FIFO

The memory address of the first-in entry in the TX FIFO is computed by the following

equation:

The memory address of the last-in entry in the TX FIFO is computed by the following

equation:

Initialization/application information

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1178 NXP Semiconductors

Loading...

Loading...