40.3.4 Timer Control Register (PIT_TCTRLn)

These registers contain the control bits for each timer.

Access: User read/write

Address: 4003_7000h base + 108h offset + (16d × i), where i=0d to 3d

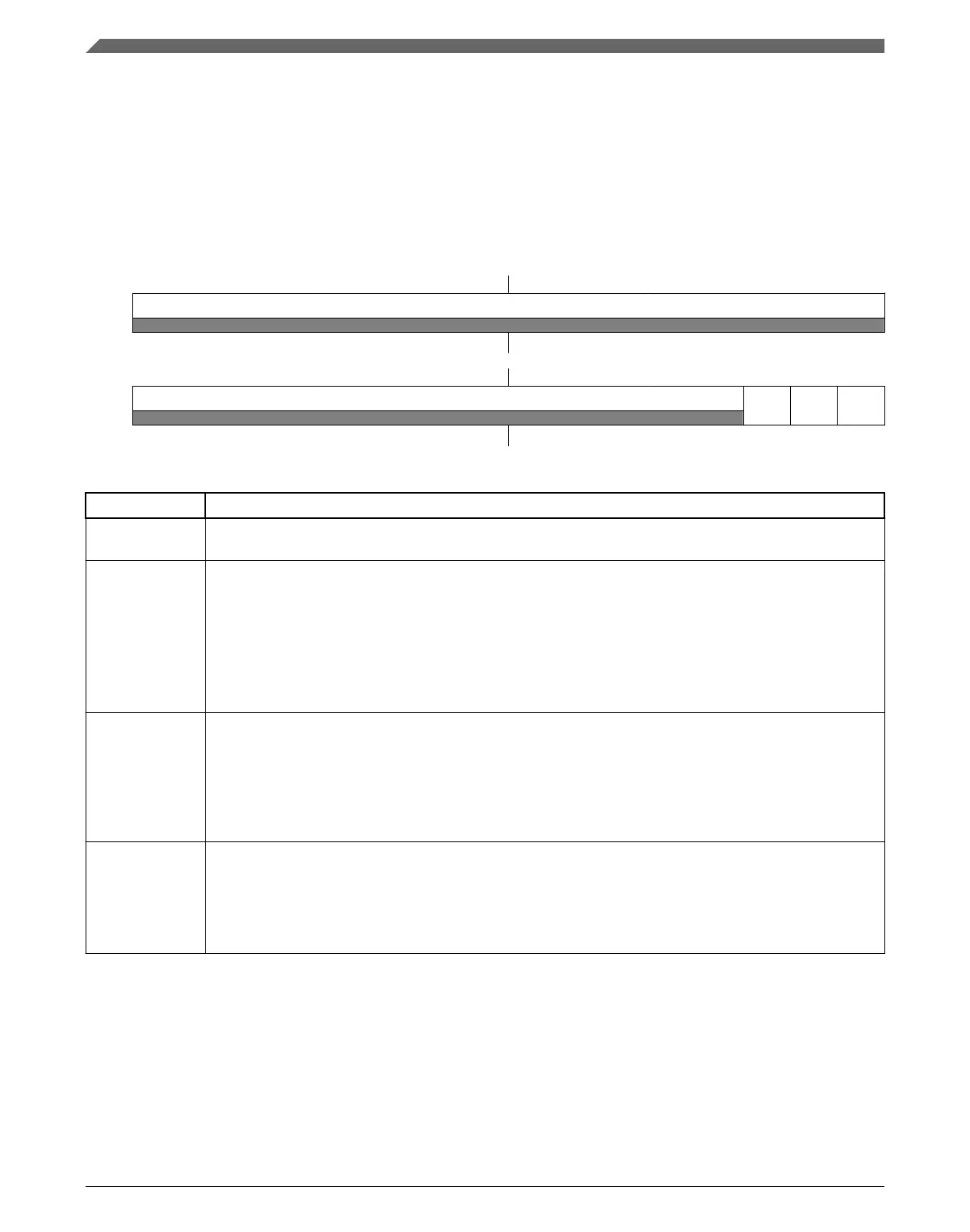

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

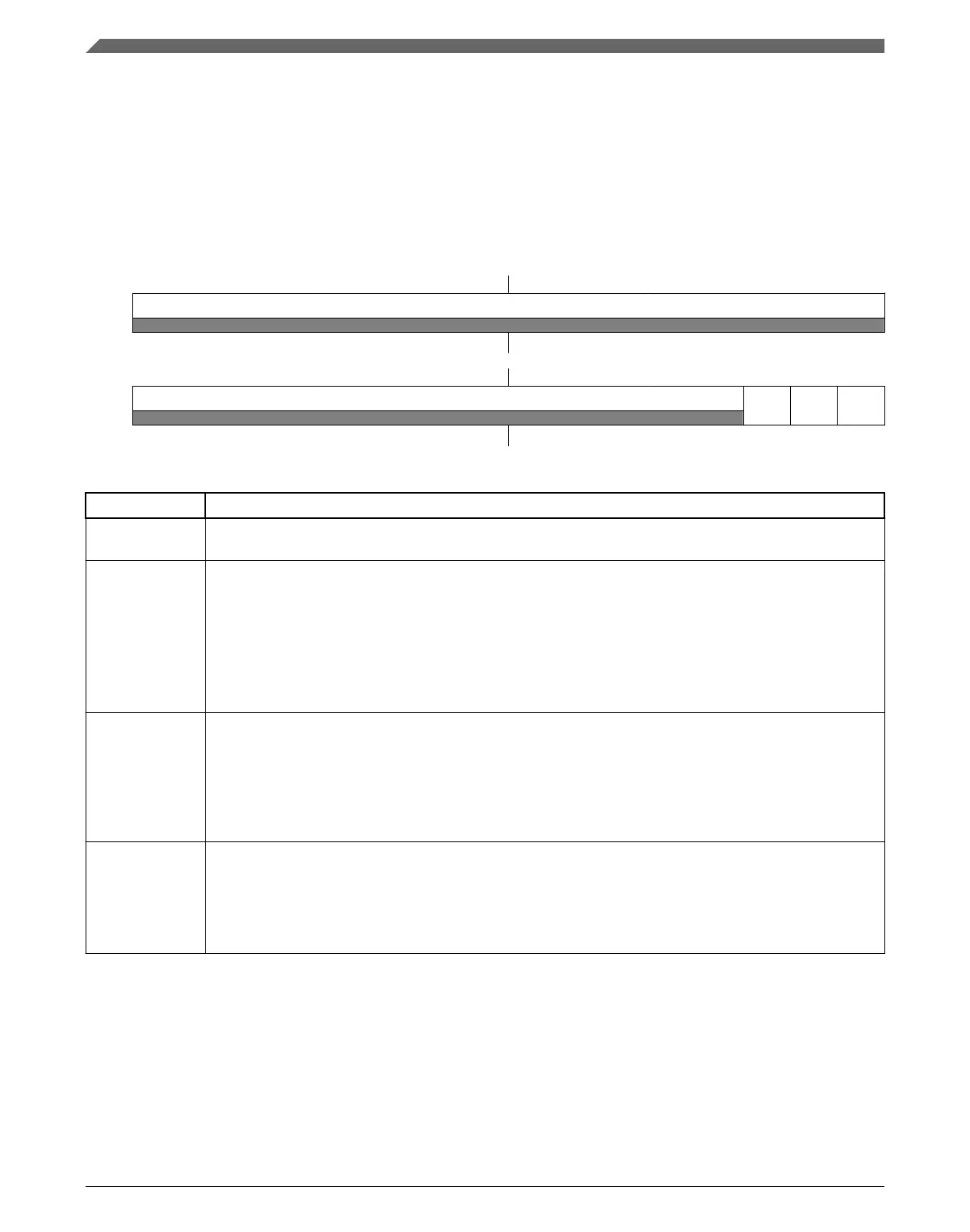

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

CHN TIE TEN

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

PIT_TCTRLn field descriptions

Field Description

31–3

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

2

CHN

Chain Mode

When activated, Timer n-1 needs to expire before timer n can decrement by 1.

Timer 0 cannot be chained.

0 Timer is not chained.

1 Timer is chained to previous timer. For example, for Channel 2, if this field is set, Timer 2 is chained to

Timer 1.

1

TIE

Timer Interrupt Enable

When an interrupt is pending, or, TFLGn[TIF] is set, enabling the interrupt will immediately cause an

interrupt event. To avoid this, the associated TFLGn[TIF] must be cleared first.

0 Interrupt requests from Timer n are disabled.

1 Interrupt will be requested whenever TIF is set.

0

TEN

Timer Enable

Enables or disables the timer.

0 Timer n is disabled.

1 Timer n is enabled.

40.3.5 Timer Flag Register (PIT_TFLGn)

These registers hold the PIT interrupt flags.

Access: User read/write

Memory map/register description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1034 NXP Semiconductors

Loading...

Loading...