LPUARTx_BAUD field descriptions (continued)

Field Description

0 One stop bit.

1 Two stop bits.

SBR Baud Rate Modulo Divisor.

The 13 bits in SBR[12:0] set the modulo divide rate for the baud rate generator. When SBR is 1 - 8191,

the baud rate equals "baud clock / ((OSR+1) × SBR)". The 13-bit baud rate setting [SBR12:SBR0] must

only be updated when the transmitter and receiver are both disabled (LPUART_CTRL[RE] and

LPUART_CTRL[TE] are both 0).

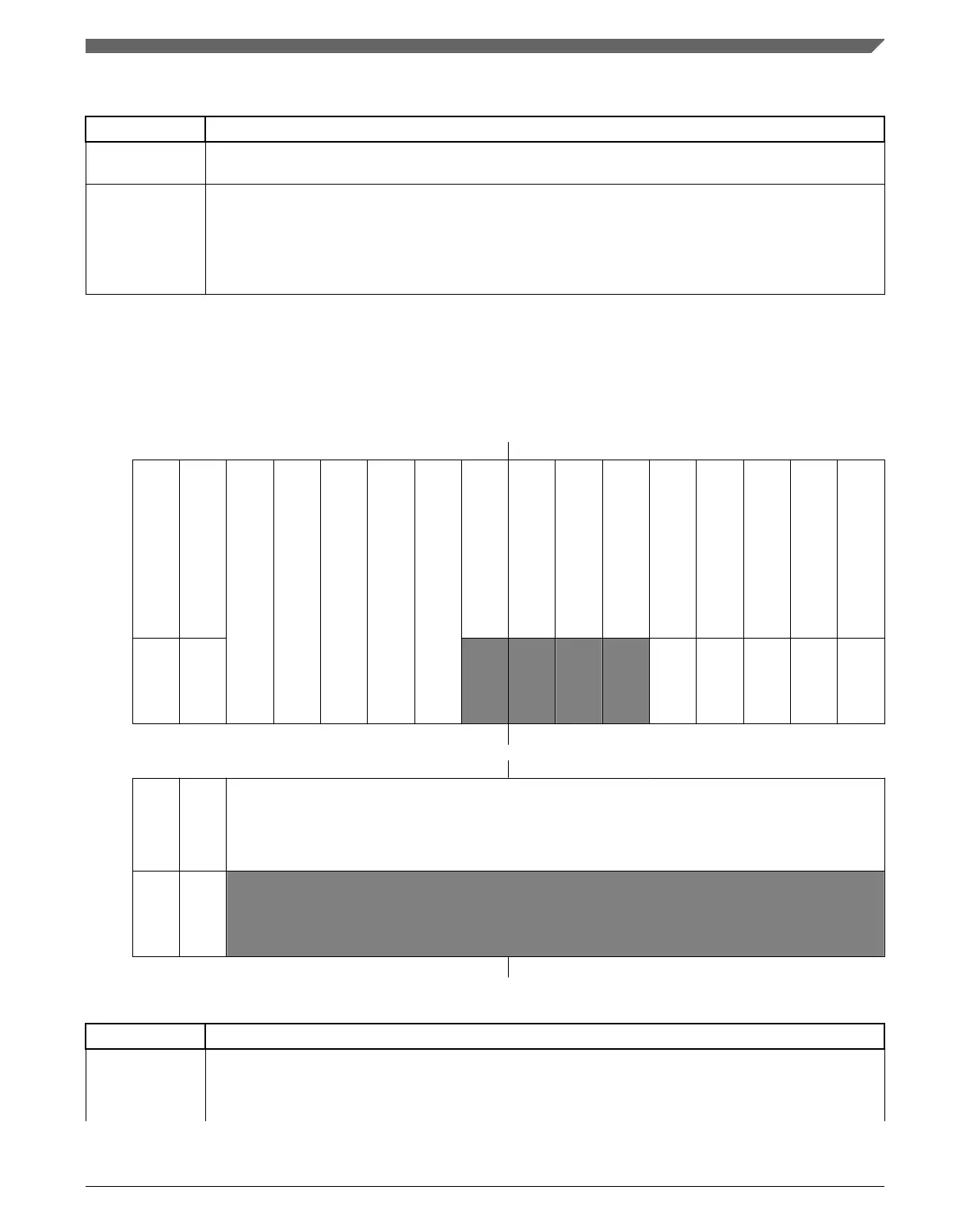

48.2.2 LPUART Status Register (LPUARTx_STAT)

Address: 4002_A000h base + 4h offset = 4002_A004h

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

LBKDIF

RXEDGIF

MSBF

RXINV

RWUID

BRK13

LBKDE

RAF

TDRE

TC

RDRF

IDLE

OR

NF

FE

PF

W

w1c

w1c

w1c w1c w1c w1c w1c

Reset

0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

MA1F

MA2F

0

W

w1c w1c

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

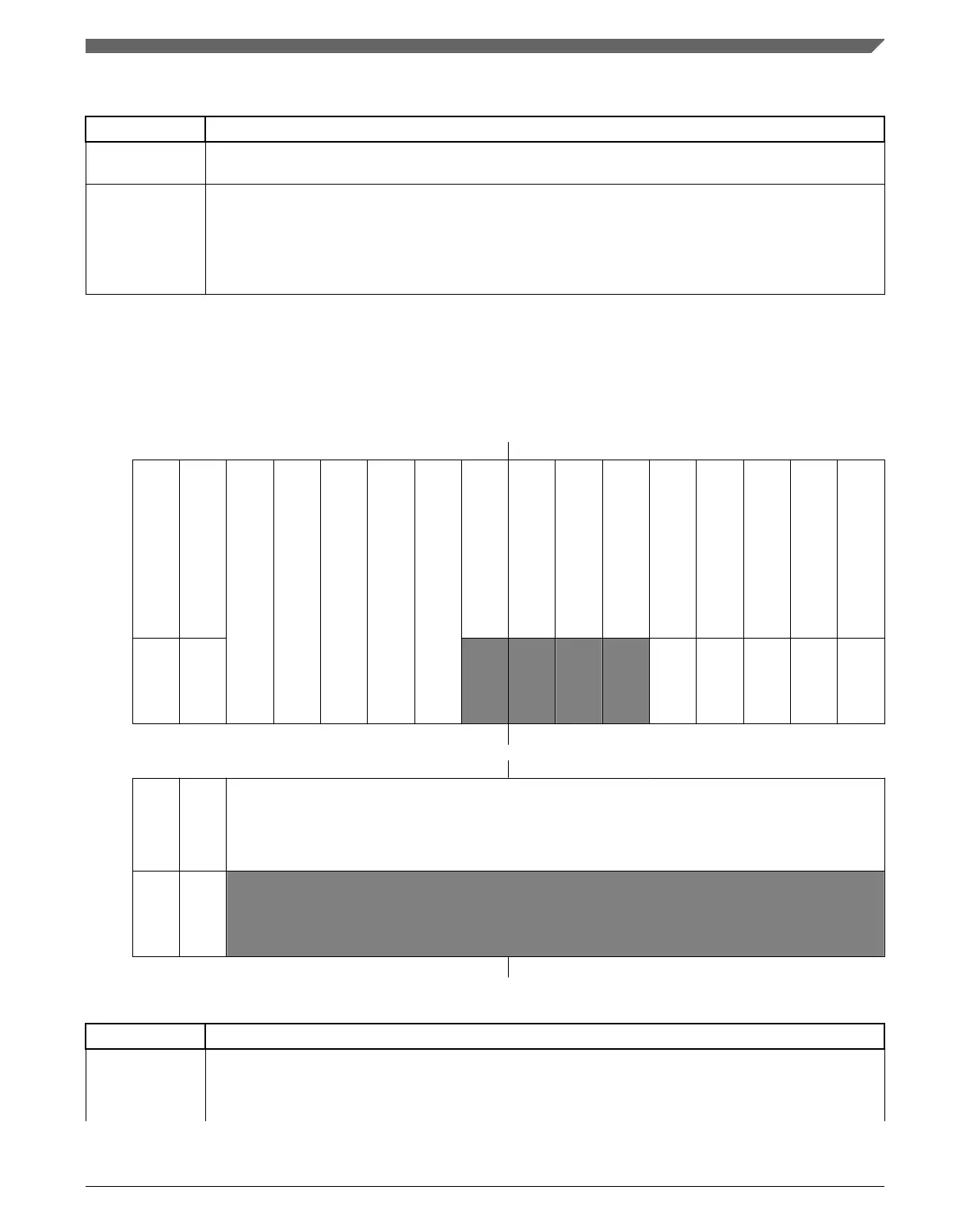

LPUARTx_STAT field descriptions

Field Description

31

LBKDIF

LIN Break Detect Interrupt Flag

LBKDIF is set when the LIN break detect circuitry is enabled and a LIN break character is detected.

LBKDIF is cleared by writing a 1 to it.

Table continues on the next page...

Chapter 48 Low Power Universal Asynchronous Receiver/Transmitter (LPUART)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1309

Loading...

Loading...