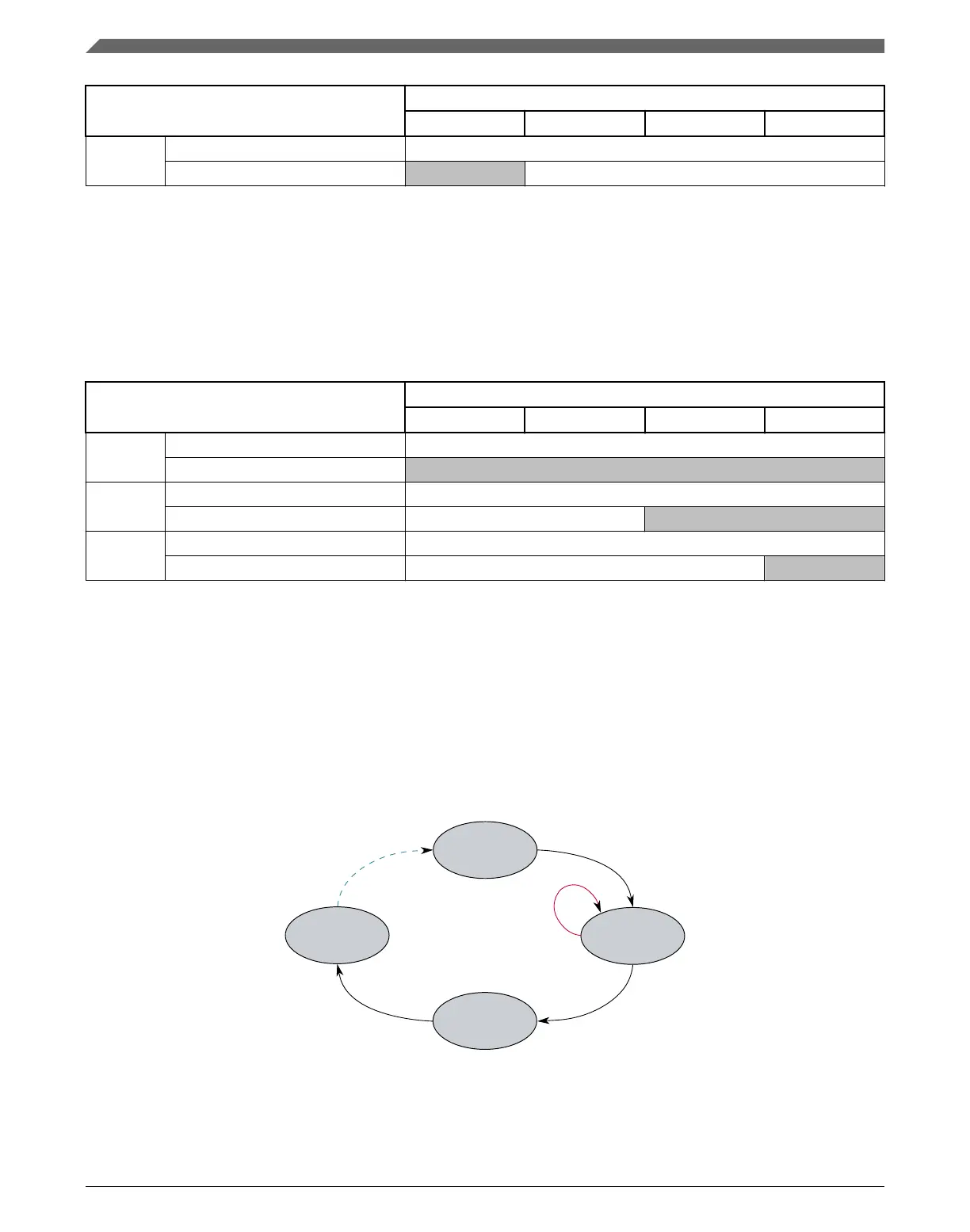

Port size and phase

FB_AD

31–24 23–16 15–8 7–0

8-bit

Address phase Address

Data phase Data Address

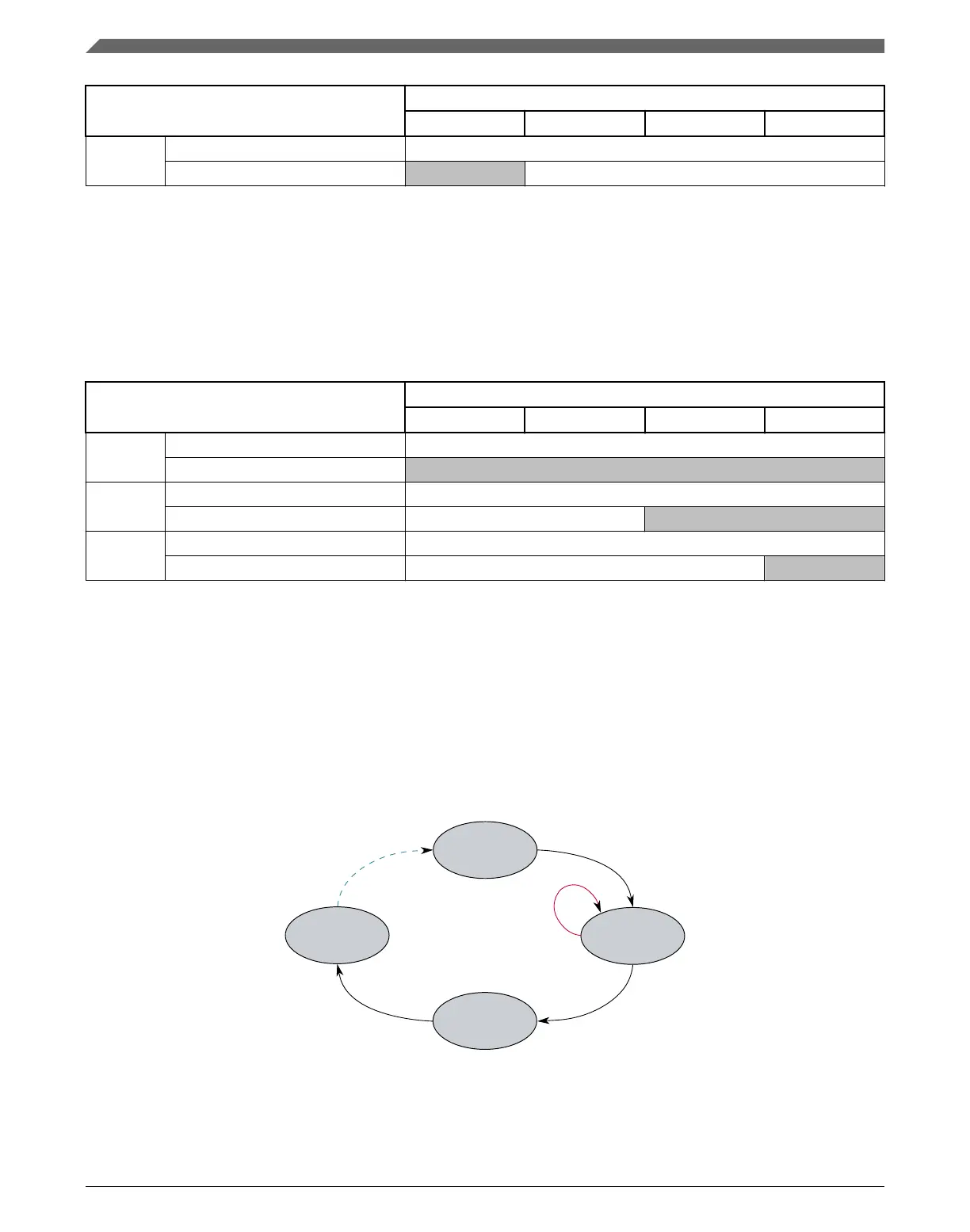

31.4.9.2 FlexBus multiplexed operating modes for CSCRn[BLS]=1

This table shows the supported combinations of address and data bus widths when

CSCRn[BLS] is 1b.

Port size and phase

FB_AD

31–24 23–16 15–8 7–0

32-bit

Address phase Address

Data phase Data

16-bit

Address phase Address

Data phase Address Data

8-bit

Address phase Address

Data phase Address Data

31.4.10 Data transfer states

Basic data transfers occur in four clocks or states. (See Figure 31-4 and Figure 31-6 for

examples of basic data transfers.) The FlexBus state machine controls the data-transfer

operation. This figure shows the state-transition diagram for basic read and write cycles.

S0

S1

S2

Wait States

S3

Next Cycle

The states are described in this table.

Functional description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

708 NXP Semiconductors

Loading...

Loading...