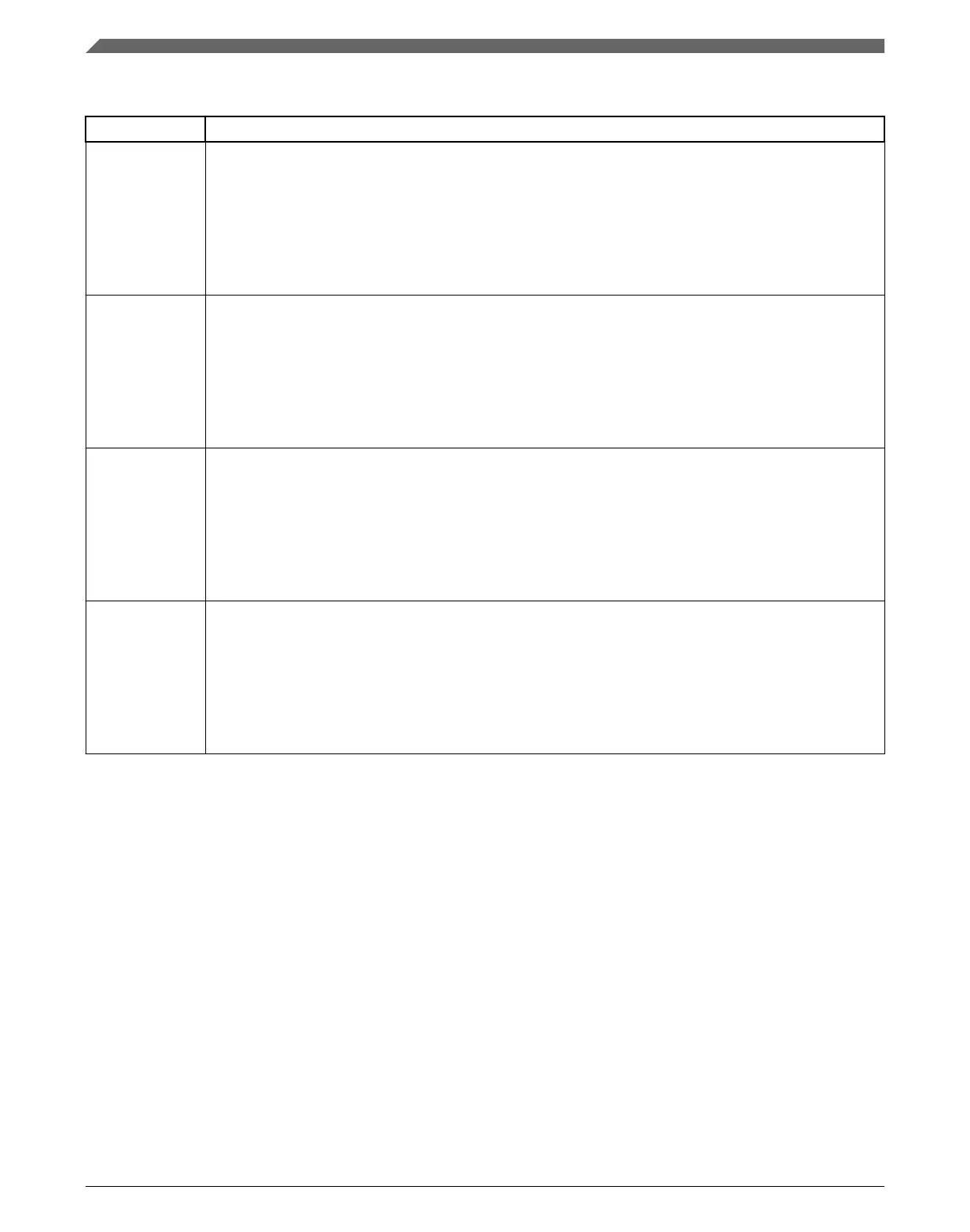

LLWU_PE3 field descriptions

Field Description

7–6

WUPE11

Wakeup Pin Enable For LLWU_P11

Enables and configures the edge detection for the wakeup pin.

00 External input pin disabled as wakeup input

01 External input pin enabled with rising edge detection

10 External input pin enabled with falling edge detection

11 External input pin enabled with any change detection

5–4

WUPE10

Wakeup Pin Enable For LLWU_P10

Enables and configures the edge detection for the wakeup pin.

00 External input pin disabled as wakeup input

01 External input pin enabled with rising edge detection

10 External input pin enabled with falling edge detection

11 External input pin enabled with any change detection

3–2

WUPE9

Wakeup Pin Enable For LLWU_P9

Enables and configures the edge detection for the wakeup pin.

00 External input pin disabled as wakeup input

01 External input pin enabled with rising edge detection

10 External input pin enabled with falling edge detection

11 External input pin enabled with any change detection

WUPE8 Wakeup Pin Enable For LLWU_P8

Enables and configures the edge detection for the wakeup pin.

00 External input pin disabled as wakeup input

01 External input pin enabled with rising edge detection

10 External input pin enabled with falling edge detection

11 External input pin enabled with any change detection

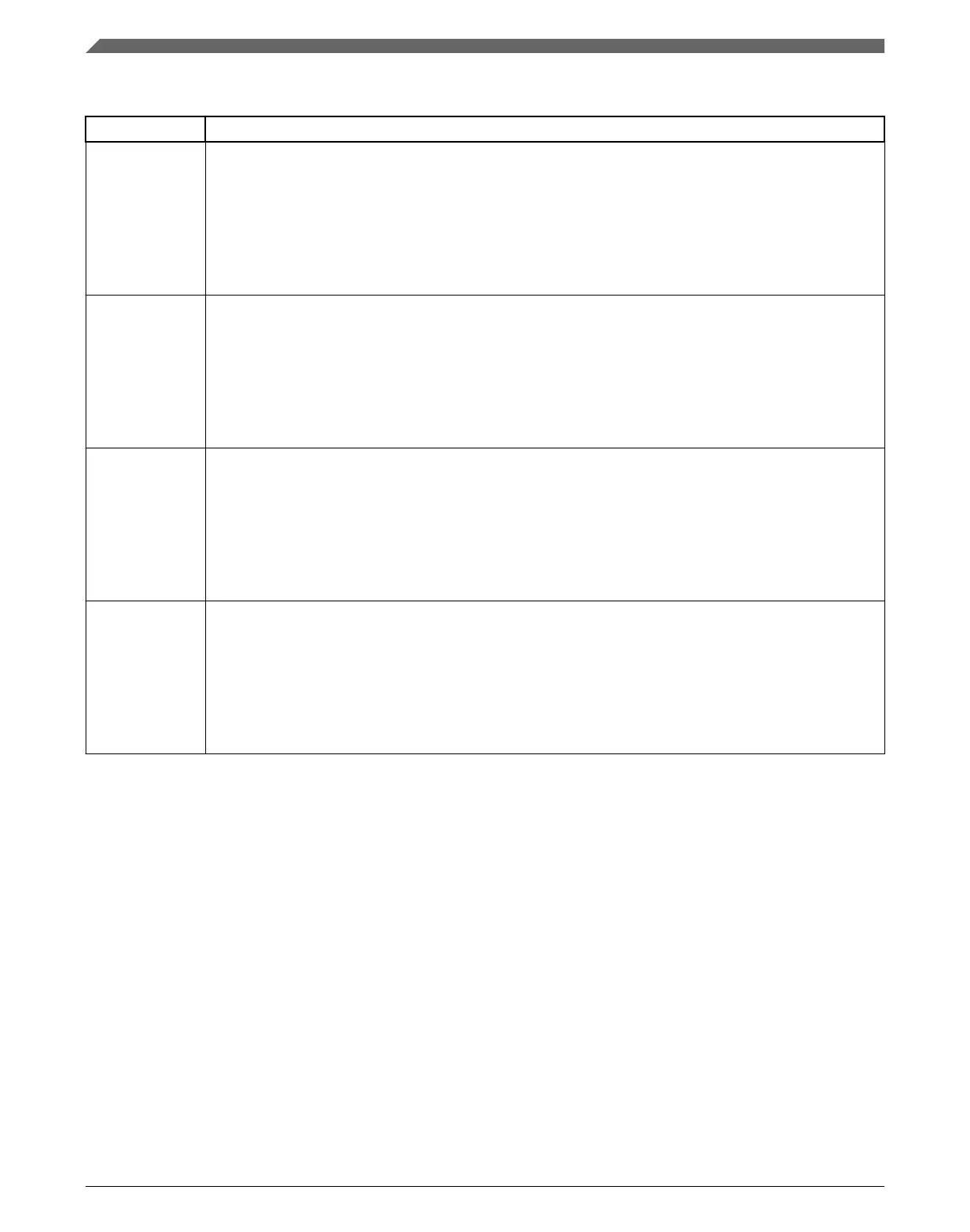

17.3.4 LLWU Pin Enable 4 register (LLWU_PE4)

LLWU_PE4 contains the field to enable and select the edge detect type for the external

wakeup input pins LLWU_P15–LLWU_P12.

NOTE

This register is reset on Chip Reset not VLLS and by reset

types that trigger Chip Reset not VLLS. It is unaffected by reset

types that do not trigger Chip Reset not VLLS. See the

Introduction details for more information.

Memory map/register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

386 NXP Semiconductors

Loading...

Loading...