DMA_ES field descriptions (continued)

Field Description

• TCDn_CITER[CITER] is equal to zero, or

• TCDn_CITER[ELINK] is not equal to TCDn_BITER[ELINK]

2

SGE

Scatter/Gather Configuration Error

0 No scatter/gather configuration error

1 The last recorded error was a configuration error detected in the TCDn_DLASTSGA field. This field is

checked at the beginning of a scatter/gather operation after major loop completion if TCDn_CSR[ESG]

is enabled. TCDn_DLASTSGA is not on a 32 byte boundary.

1

SBE

Source Bus Error

0 No source bus error

1 The last recorded error was a bus error on a source read

0

DBE

Destination Bus Error

0 No destination bus error

1 The last recorded error was a bus error on a destination write

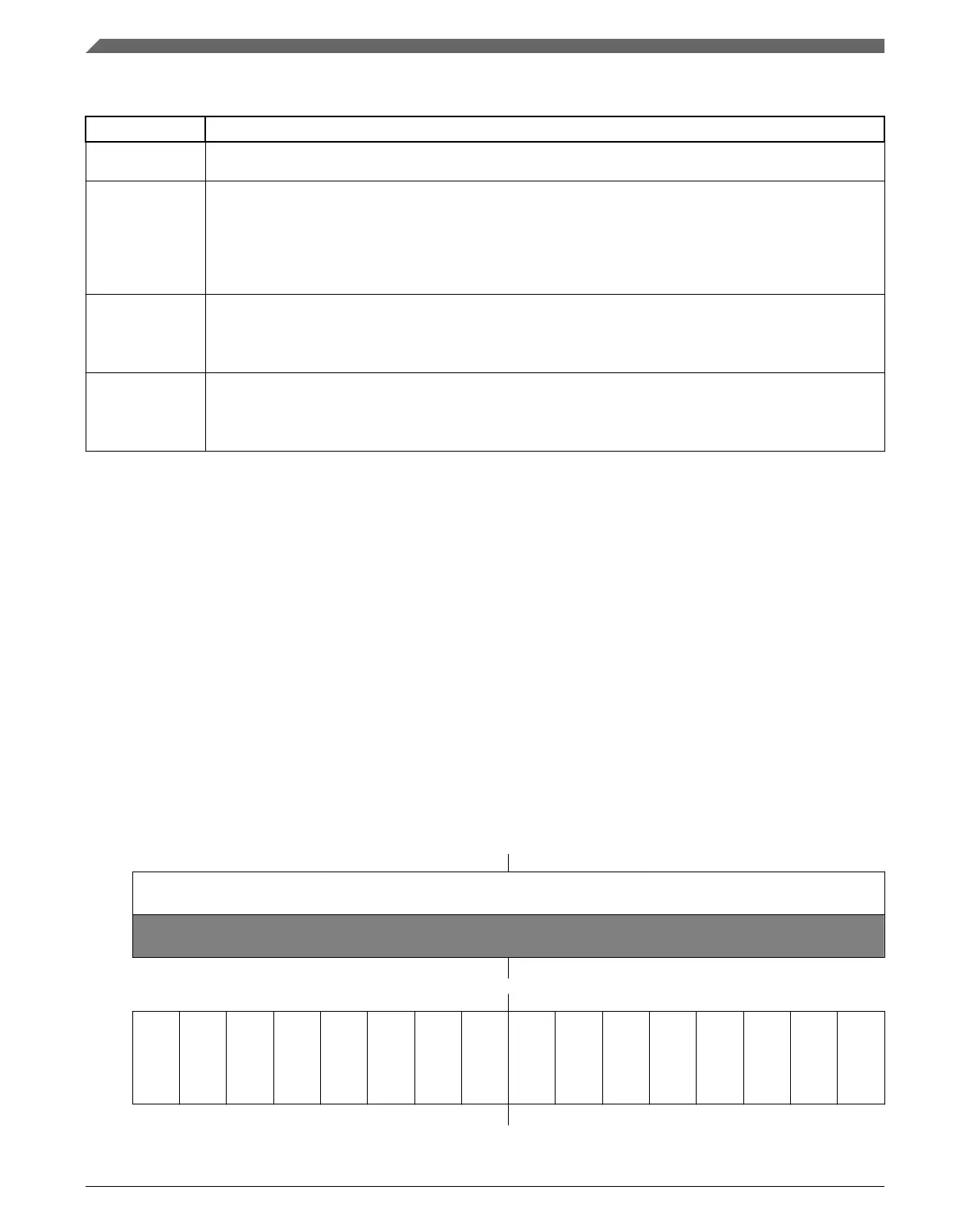

22.3.7 Enable Request Register (DMA_ERQ)

The ERQ register provides a bit map for the 16 channels to enable the request signal for

each channel. The state of any given channel enable is directly affected by writes to this

register; it is also affected by writes to the SERQ and CERQ registers. These registers are

provided so the request enable for a single channel can easily be modified without

needing to perform a read-modify-write sequence to the ERQ.

DMA request input signals and this enable request flag must be asserted before a

channel’s hardware service request is accepted. The state of the DMA enable request flag

does not affect a channel service request made explicitly through software or a linked

channel request.

Address:

4000_8000h base + Ch offset = 4000_800Ch

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

ERQ15

ERQ14

ERQ13

ERQ12

ERQ11

ERQ10

ERQ9 ERQ8 ERQ7 ERQ6 ERQ5 ERQ4 ERQ3 ERQ2 ERQ1 ERQ0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Memory map/register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

446 NXP Semiconductors

Loading...

Loading...