FTMx_CONF field descriptions (continued)

Field Description

Selects the ratio between the number of counter overflows to the number of times the TOF bit is set.

NUMTOF = 0: The TOF bit is set for each counter overflow.

NUMTOF = 1: The TOF bit is set for the first counter overflow but not for the next overflow.

NUMTOF = 2: The TOF bit is set for the first counter overflow but not for the next 2 overflows.

NUMTOF = 3: The TOF bit is set for the first counter overflow but not for the next 3 overflows.

This pattern continues up to a maximum of 31.

39.3.23 FTM Fault Input Polarity (FTMx_FLTPOL)

This register defines the fault inputs polarity.

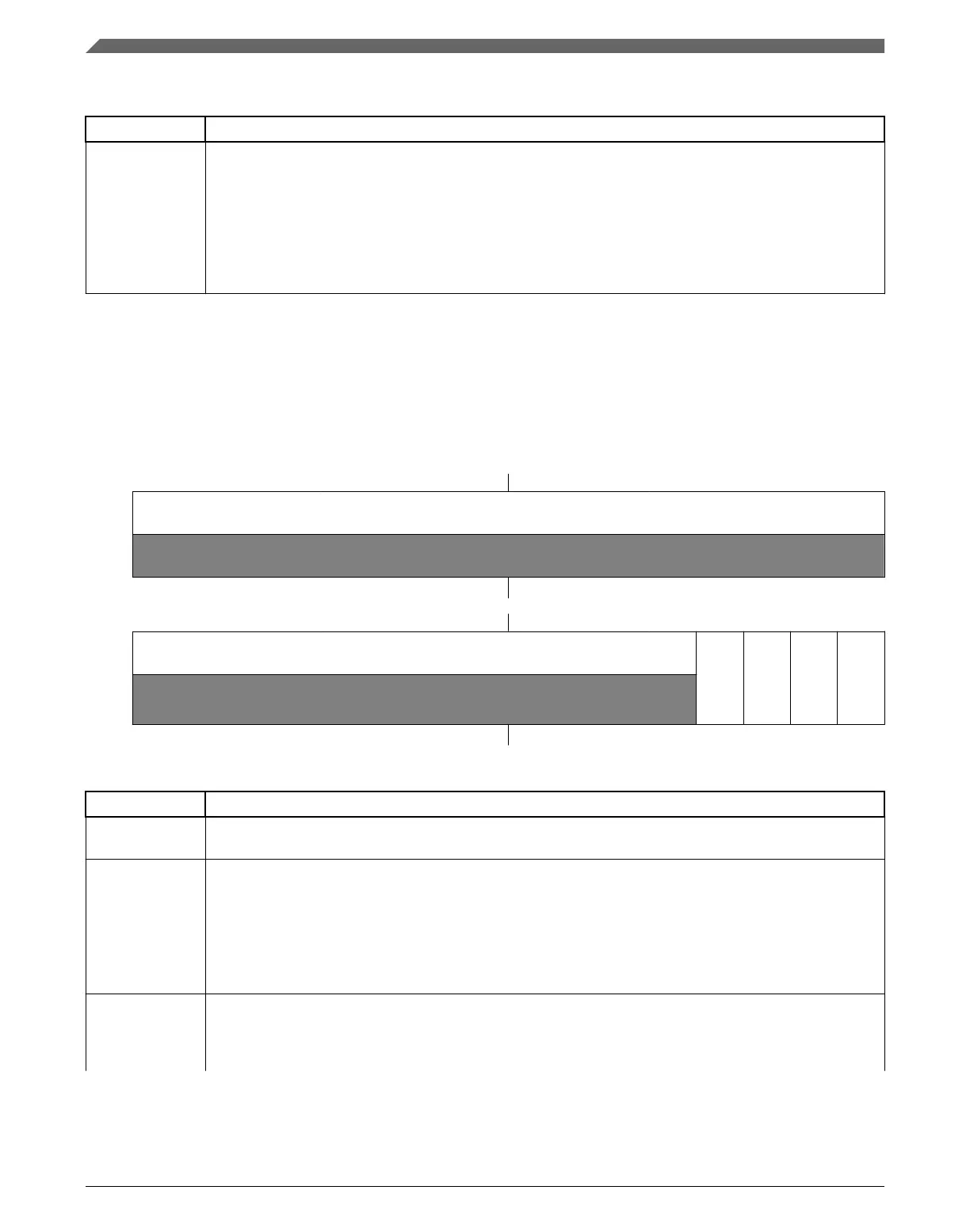

Address:

Base address + 88h offset

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R

0

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0

FLT3POL

FLT2POL

FLT1POL

FLT0POL

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

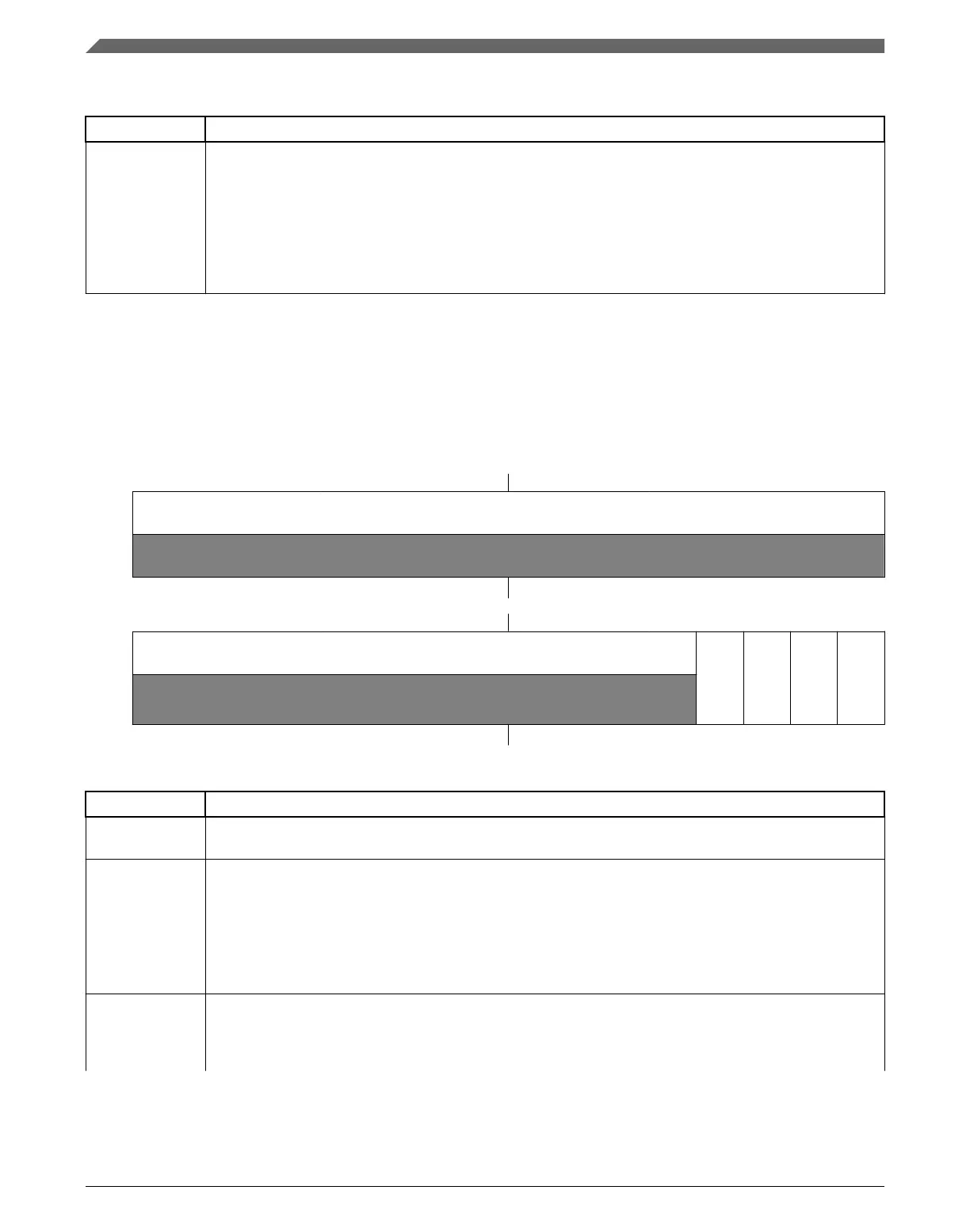

FTMx_FLTPOL field descriptions

Field Description

31–4

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

3

FLT3POL

Fault Input 3 Polarity

Defines the polarity of the fault input.

This field is write protected. It can be written only when MODE[WPDIS] = 1.

0 The fault input polarity is active high. A 1 at the fault input indicates a fault.

1 The fault input polarity is active low. A 0 at the fault input indicates a fault.

2

FLT2POL

Fault Input 2 Polarity

Defines the polarity of the fault input.

This field is write protected. It can be written only when MODE[WPDIS] = 1.

Table continues on the next page...

Memory map and register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

938 NXP Semiconductors

Loading...

Loading...