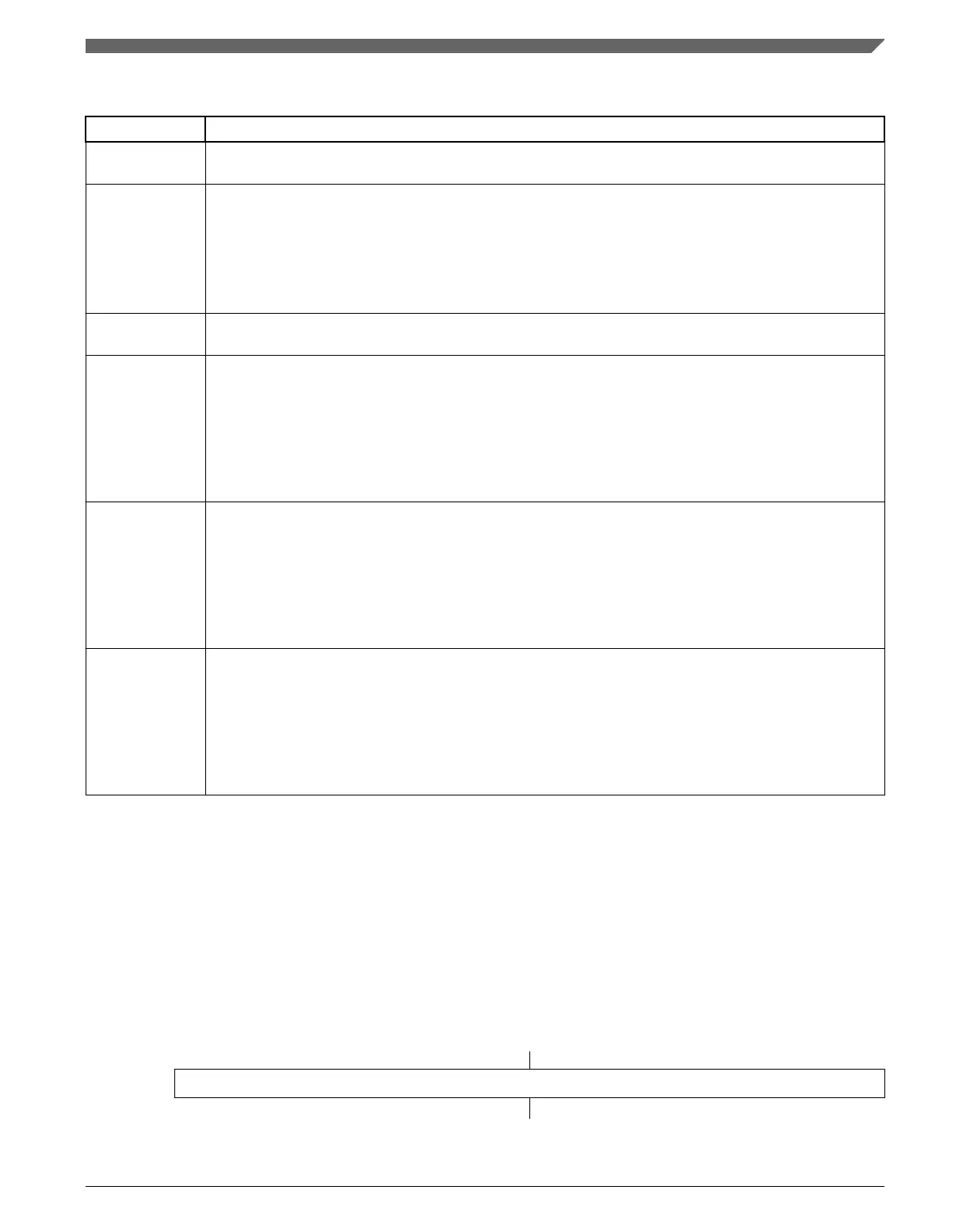

UARTx_SFIFO field descriptions (continued)

Field Description

0 Transmit buffer is not empty.

1 Transmit buffer is empty.

6

RXEMPT

Receive Buffer/FIFO Empty

Asserts when there is no data in the receive FIFO/Buffer. This field does not take into account data that is

in the receive shift register.

0 Receive buffer is not empty.

1 Receive buffer is empty.

5–3

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

2

RXOF

Receiver Buffer Overflow Flag

Indicates that more data has been written to the receive buffer than it can hold. This field will assert

regardless of the value of CFIFO[RXOFE]. However, an interrupt will be issued to the host only if

CFIFO[RXOFE] is set. This flag is cleared by writing a 1.

0 No receive buffer overflow has occurred since the last time the flag was cleared.

1 At least one receive buffer overflow has occurred since the last time the flag was cleared.

1

TXOF

Transmitter Buffer Overflow Flag

Indicates that more data has been written to the transmit buffer than it can hold. This field will assert

regardless of the value of CFIFO[TXOFE]. However, an interrupt will be issued to the host only if

CFIFO[TXOFE] is set. This flag is cleared by writing a 1.

0 No transmit buffer overflow has occurred since the last time the flag was cleared.

1 At least one transmit buffer overflow has occurred since the last time the flag was cleared.

0

RXUF

Receiver Buffer Underflow Flag

Indicates that more data has been read from the receive buffer than was present. This field will assert

regardless of the value of CFIFO[RXUFE]. However, an interrupt will be issued to the host only if

CFIFO[RXUFE] is set. This flag is cleared by writing a 1.

0 No receive buffer underflow has occurred since the last time the flag was cleared.

1 At least one receive buffer underflow has occurred since the last time the flag was cleared.

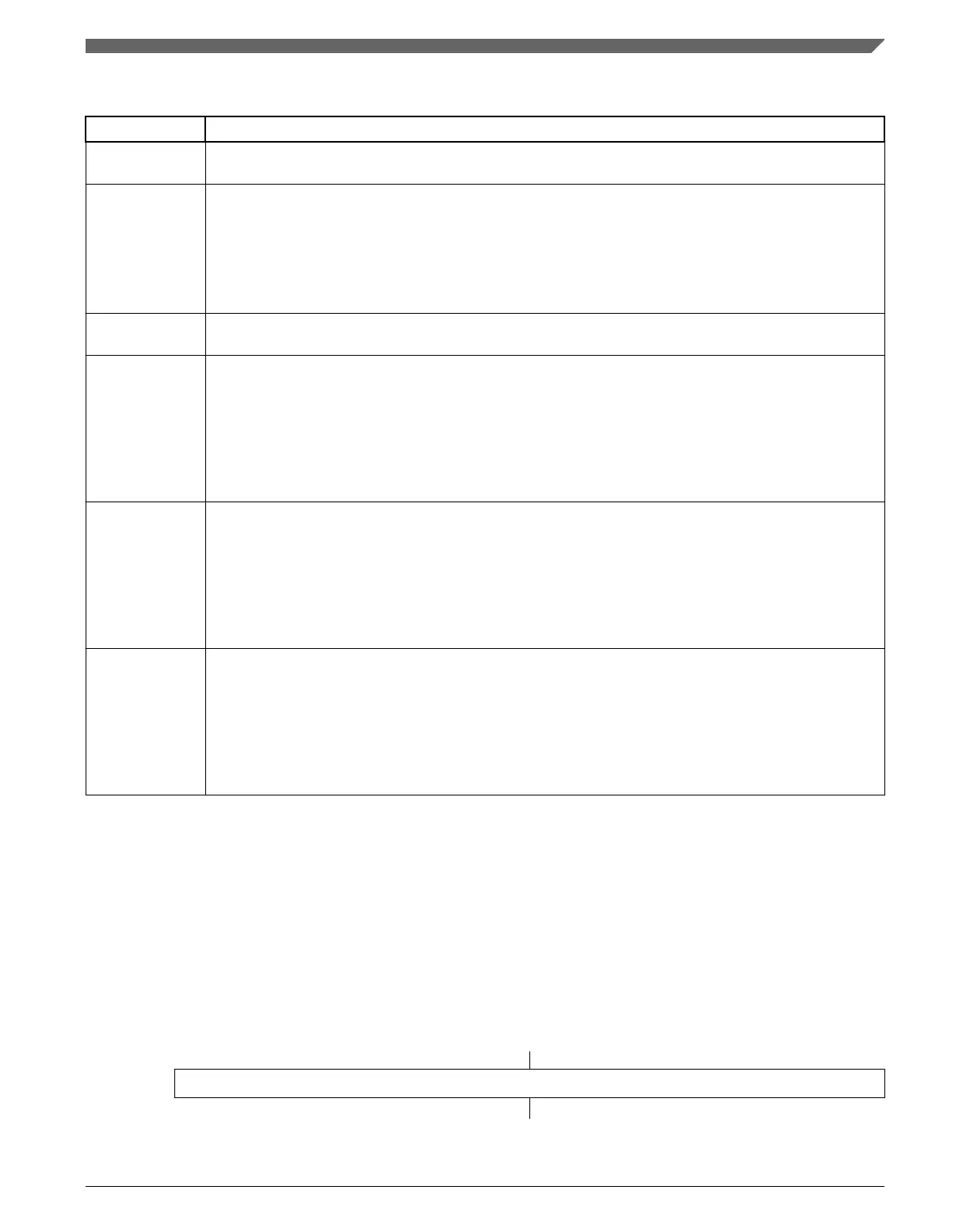

47.3.19 UART FIFO Transmit Watermark (UARTx_TWFIFO)

This register provides the ability to set a programmable threshold for notification of

needing additional transmit data. This register may be read at any time but must be

written only when C2[TE] is not set. Changing the value of the watermark will not clear

the S1[TDRE] flag.

Address:

Base address + 13h offset

Bit 7 6 5 4 3 2 1 0

Read

TXWATER

Write

Reset

0 0 0 0 0 0 0 0

Chapter 47 Universal Asynchronous Receiver/Transmitter (UART)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1245

Loading...

Loading...