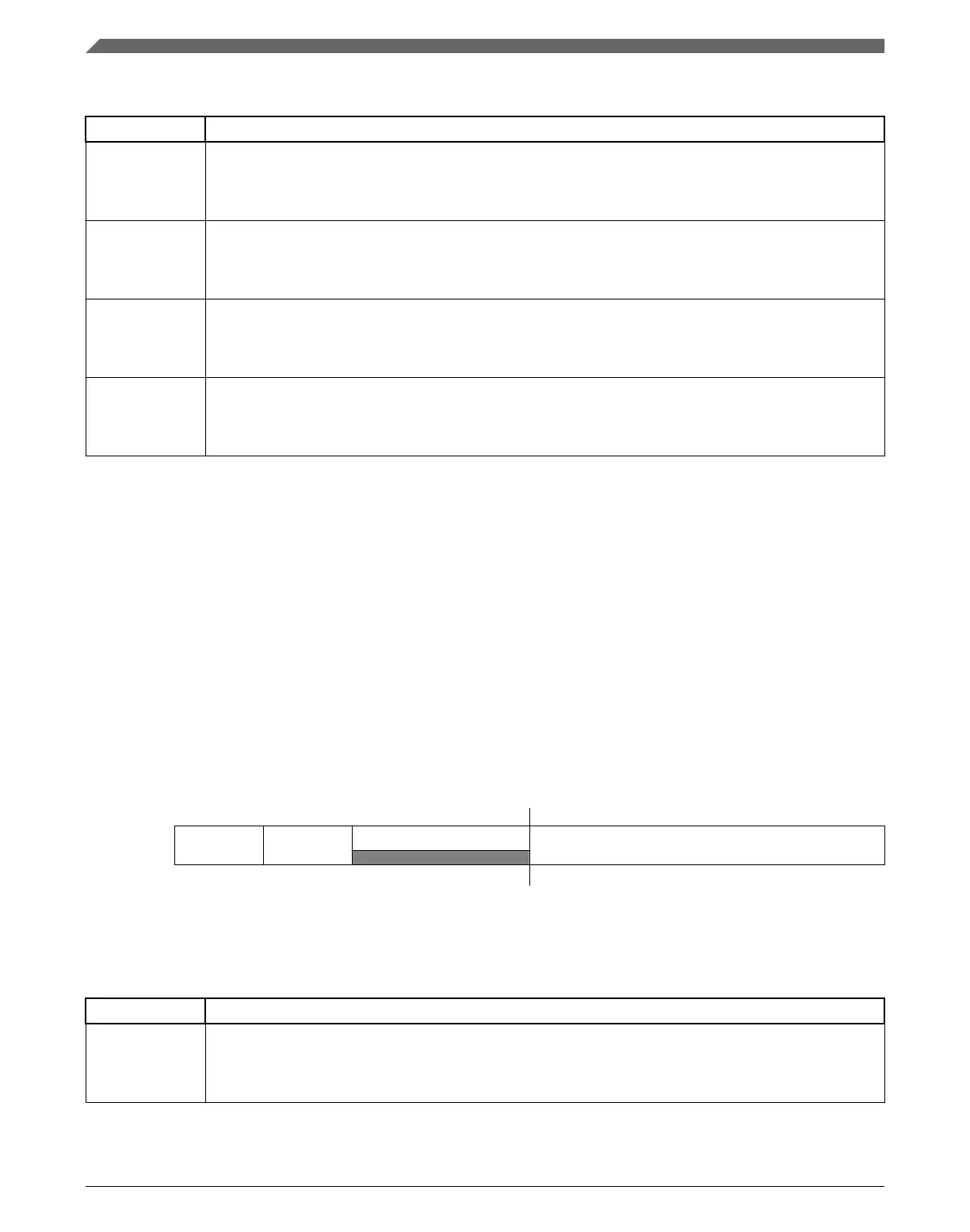

DMA_EARS field descriptions (continued)

Field Description

3

EDREQ_3

Enable asynchronous DMA request in stop mode for channel 3.

0 Disable asynchronous DMA request for channel 3.

1 Enable asynchronous DMA request for channel 3.

2

EDREQ_2

Enable asynchronous DMA request in stop mode for channel 2.

0 Disable asynchronous DMA request for channel 2.

1 Enable asynchronous DMA request for channel 2.

1

EDREQ_1

Enable asynchronous DMA request in stop mode for channel 1.

0 Disable asynchronous DMA request for channel 1

1 Enable asynchronous DMA request for channel 1.

0

EDREQ_0

Enable asynchronous DMA request in stop mode for channel 0.

0 Disable asynchronous DMA request for channel 0.

1 Enable asynchronous DMA request for channel 0.

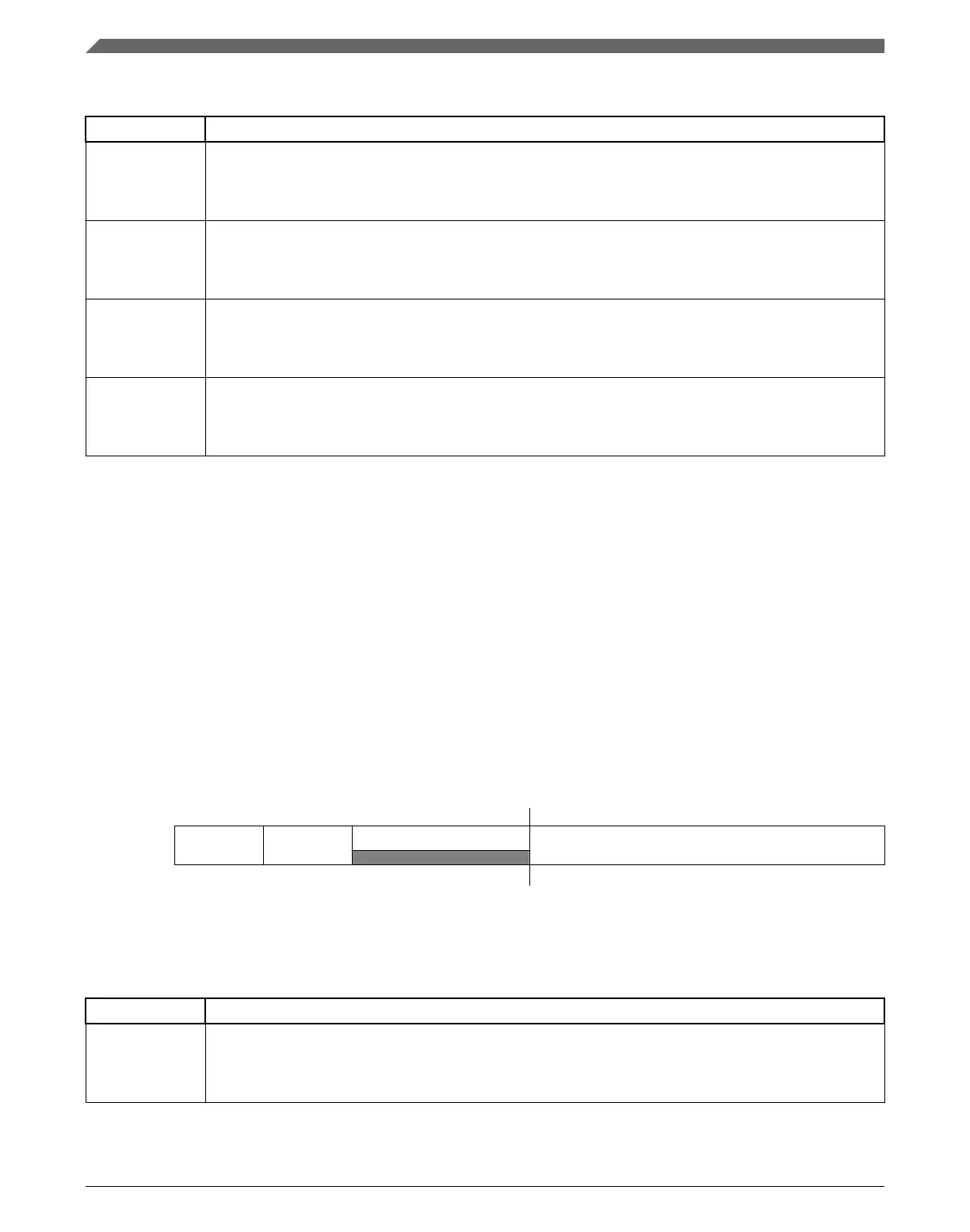

22.3.21 Channel n Priority Register (DMA_DCHPRIn)

When fixed-priority channel arbitration is enabled (CR[ERCA] = 0), the contents of these

registers define the unique priorities associated with each channel. The channel priorities

are evaluated by numeric value; for example, 0 is the lowest priority, 1 is the next higher

priority, then 2, 3, etc. Software must program the channel priorities with unique values;

otherwise, a configuration error is reported. The range of the priority value is limited to

the values of 0 through 15.

Address:

4000_8000h base + 100h offset + (1d × i), where i=0d to 15d

Bit 7 6 5 4 3 2 1 0

Read

ECP DPA

0

CHPRI

Write

Reset

0 0 0 0 * * * *

* Notes:

CHPRI field: See bit field description.•

DMA_DCHPRIn field descriptions

Field Description

7

ECP

Enable Channel Preemption.

0 Channel n cannot be suspended by a higher priority channel’s service request.

1 Channel n can be temporarily suspended by the service request of a higher priority channel.

Table continues on the next page...

Memory map/register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

468 NXP Semiconductors

Loading...

Loading...