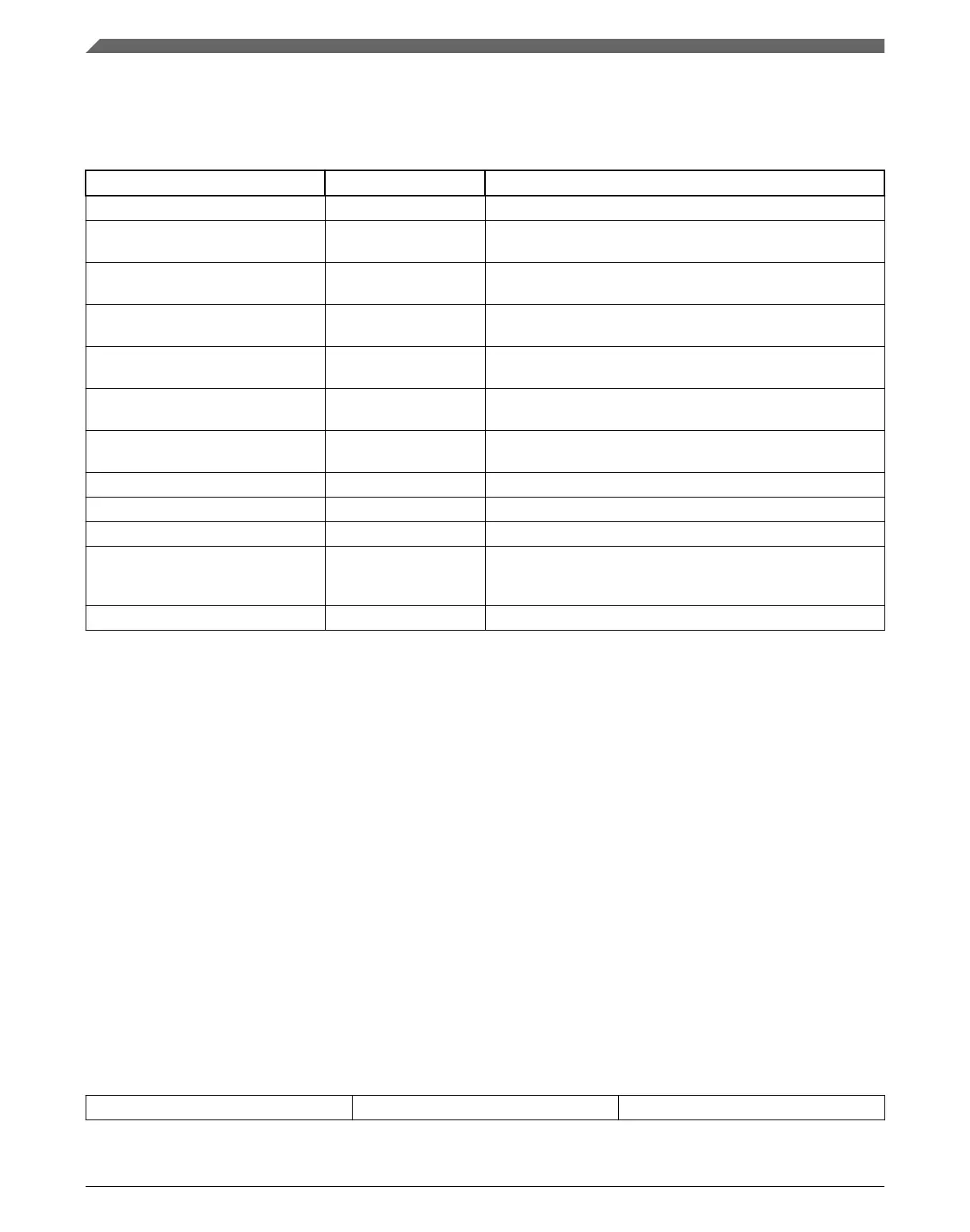

9.4.1 IR Codes

Table 9-3. JTAG Instructions

Instruction Code[3:0] Instruction Summary

IDCODE 0000 Selects device identification register for shift

SAMPLE/PRELOAD 0010 Selects boundary scan register for shifting, sampling, and

preloading without disturbing functional operation

SAMPLE 0011 Selects boundary scan register for shifting and sampling

without disturbing functional operation

EXTEST 0100 Selects boundary scan register while applying preloaded

values to output pins and asserting functional reset

HIGHZ 1001 Selects bypass register while three-stating all output pins and

asserting functional reset

CLAMP 1100 Selects bypass register while applying preloaded values to

output pins and asserting functional reset

EZPORT 1101 Enables the EZPORT function for the SoC and asserts

functional reset.

ARM_IDCODE 1110 ARM JTAG-DP Instruction

BYPASS 1111 Selects bypass register for data operations

Factory debug reserved 0101, 0110, 0111 Intended for factory debug only

ARM JTAG-DP Reserved 1000, 1010, 1011, 1110 These instructions will go the ARM JTAG-DP controller.

Please look at ARM JTAG-DP documentation for more

information on these instructions.

Reserved

3

All other opcodes Decoded to select bypass register

3. The manufacturer reserves the right to change the decoding of reserved instruction codes in the future

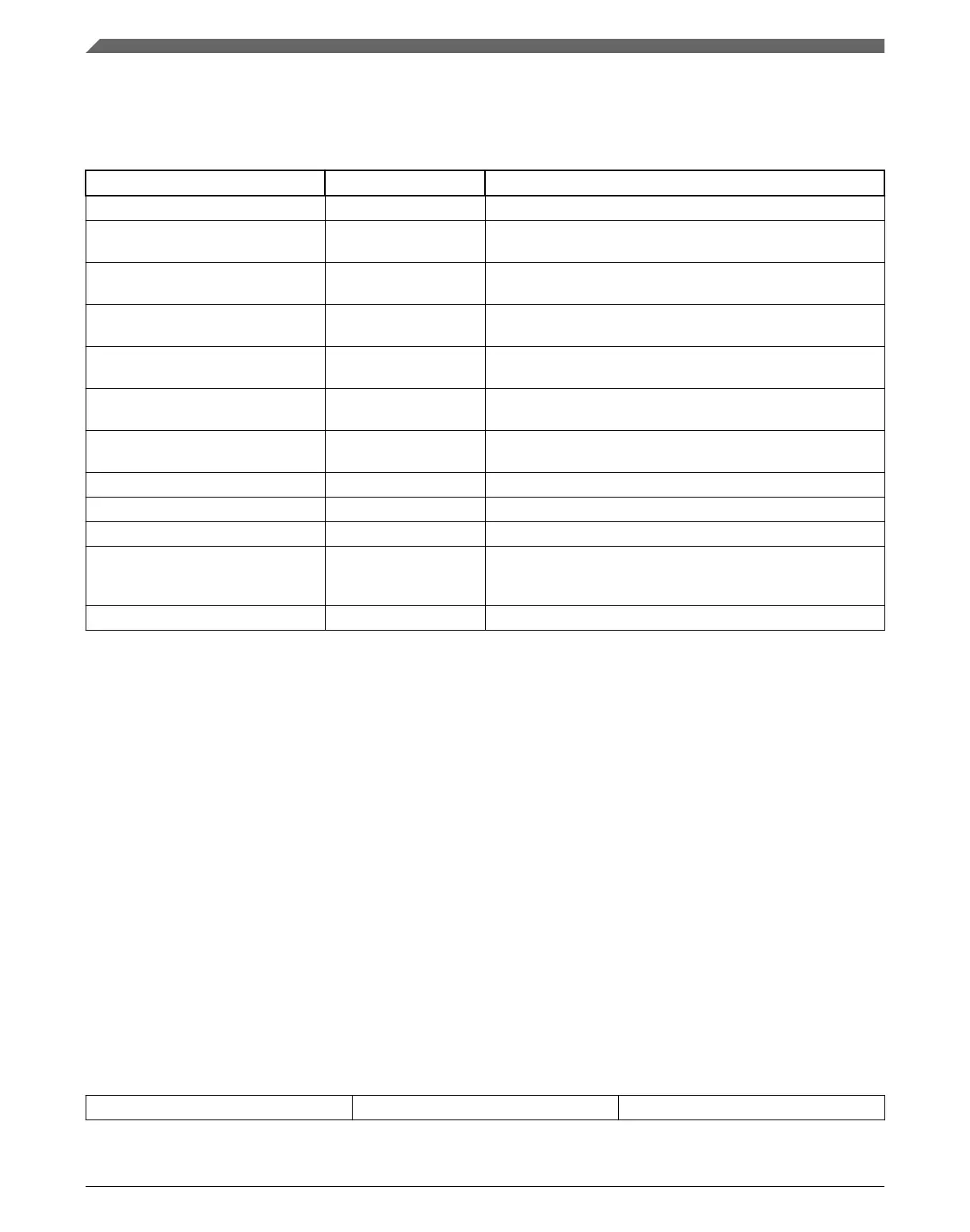

9.5 JTAG status and control registers

Through the ARM Debug Access Port (DAP), the debugger has access to the status and

control elements, implemented as registers on the DAP bus as shown in the following

figure. These registers provide additional control and status for low power mode recovery

and typical run-control scenarios. The status register bits also provide a means for the

debugger to get updated status of the core without having to initiate a bus transaction

across the crossbar switch, thus remaining less intrusive during a debug session.

It is important to note that these DAP control and status registers are not memory mapped

within the system memory map and are only accessible via the Debug Access Port (DAP)

using JTAG, cJTAG, or SWD. The MDM-AP is accessible as Debug Access Port 1 with

the available registers shown in the table below.

Table 9-4. MDM-AP Register Summary

Address Register Description

Table continues on the next page...

JTAG status and control registers

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

204 NXP Semiconductors

Loading...

Loading...