2. FB_CS3not available on 100-LQFP devices.

3. FB_BE7_0_BLS31_24not available on 100-LQFP devices.

4. FB_TAnotavailable on 100-LQFP devices.

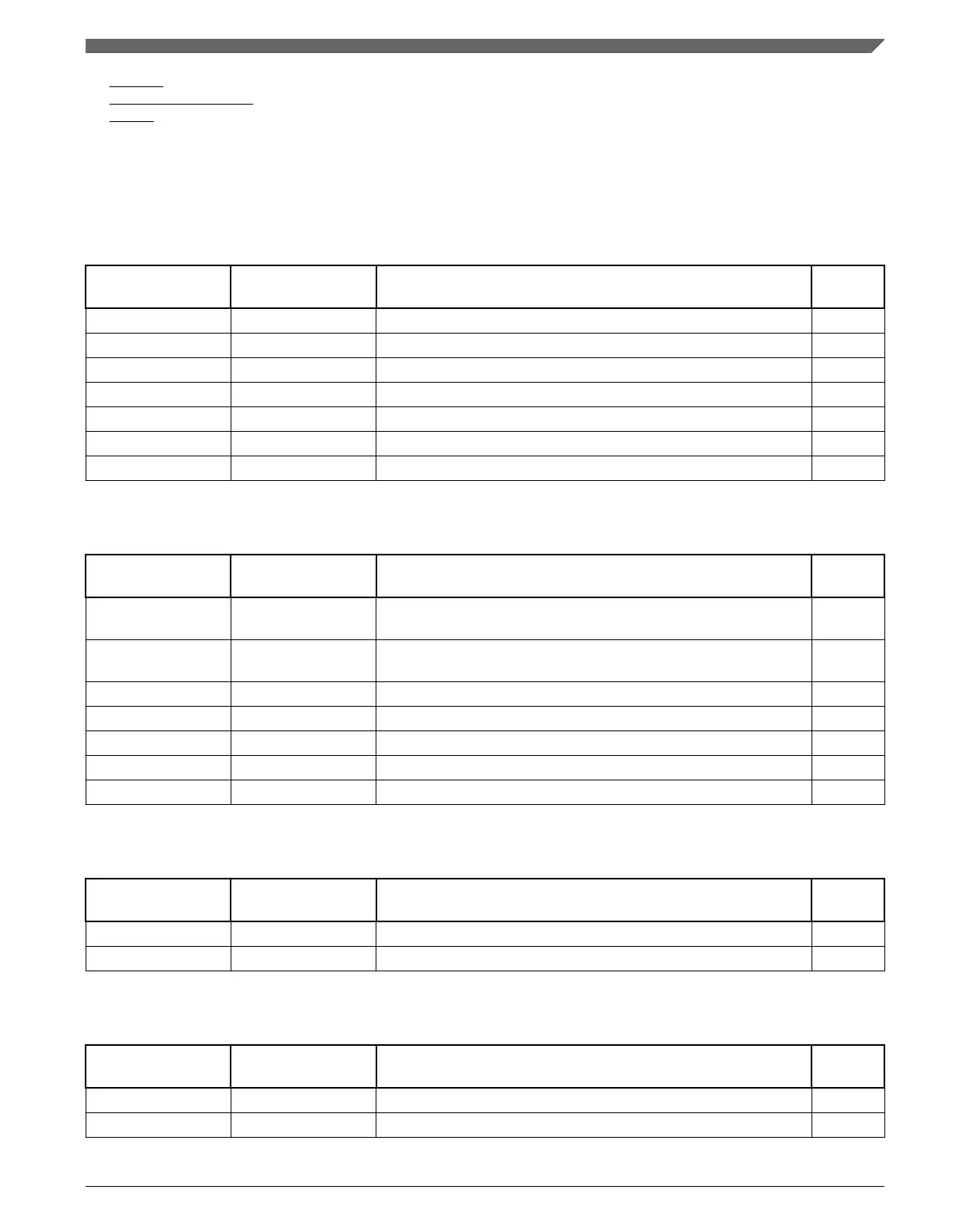

10.4.5 Analog

Table 10-11. ADC 0 Signal Descriptions

Chip signal name Module signal

name

Description I/O

ADC0_DP[3:0] DADP3–DADP0 Differential Analog Channel Inputs I

ADC0_DM[3:0] DADM3–DADM0 Differential Analog Channel Inputs I

ADC0_SEn ADn Single-Ended Analog Channel Inputs I

VREFH V

REFSH

Voltage Reference Select High I

VREFL V

REFSL

Voltage Reference Select Low I

VDDA V

DDA

Analog Power Supply I

VSSA V

SSA

Analog Ground I

Table 10-12. ADC 1 Signal Descriptions

Chip signal name Module signal

name

Description I/O

ADC1_DP3,

ADC1_DP[1:0]

DADP3–DADP0 Differential Analog Channel Inputs I

ADC1_DM3,

ADC1_DM[1:0]

DADM3–DADM0 Differential Analog Channel Inputs I

ADC1_SEn ADn Single-Ended Analog Channel Inputs I

VREFH V

REFSH

Voltage Reference Select High I

VREFL V

REFSL

Voltage Reference Select Low I

VDDA V

DDA

Analog Power Supply I

VSSA V

SSA

Analog Ground I

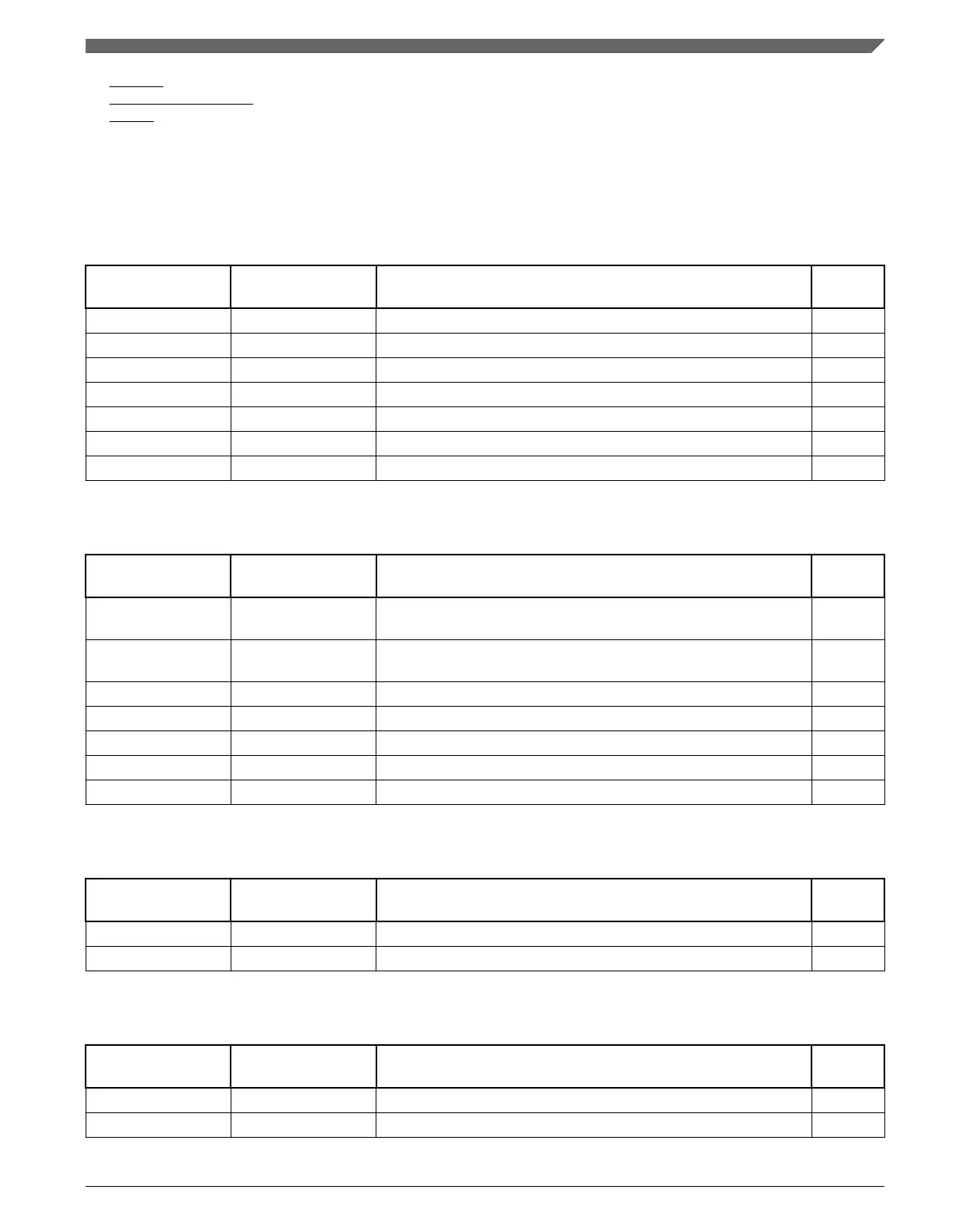

Table 10-13. CMP 0 Signal Descriptions

Chip signal name Module signal

name

Description I/O

CMP0_IN[5:0] IN[5:0] Analog voltage inputs I

CMP0_OUT CMPO Comparator output O

Table 10-14. CMP 1 Signal Descriptions

Chip signal name Module signal

name

Description I/O

CMP1_IN[5:0] IN[5:0] Analog voltage inputs I

CMP1_OUT CMPO Comparator output O

Chapter 10 Signal Multiplexing and Signal Descriptions

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 233

Loading...

Loading...