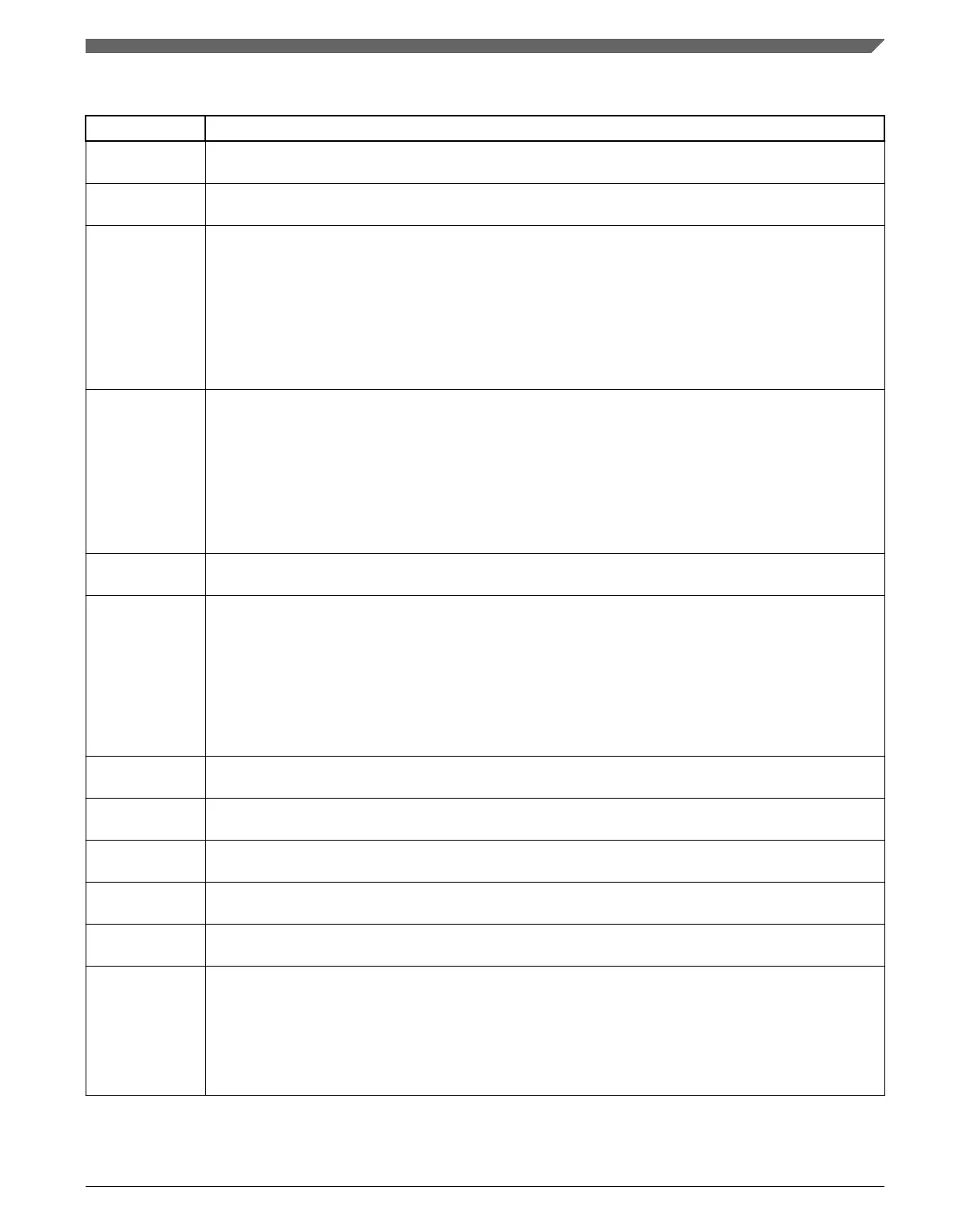

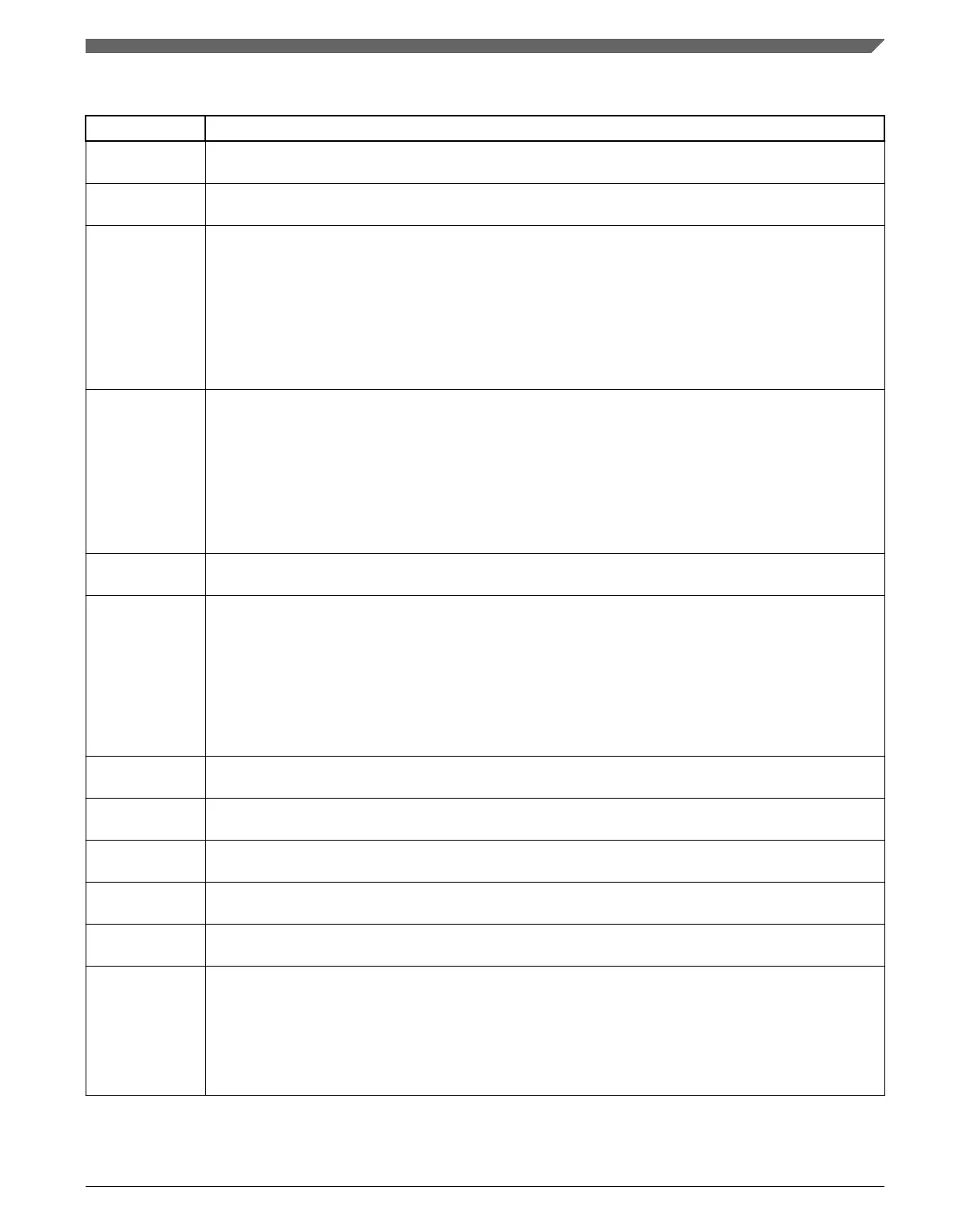

SPIx_SR field descriptions (continued)

Field Description

0 Transmit and receive operations are disabled (The module is in Stopped state).

1 Transmit and receive operations are enabled (The module is in Running state).

29

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

28

EOQF

End of Queue Flag

Indicates that the last entry in a queue has been transmitted when the module is in Master mode. The

EOQF bit is set when the TX FIFO entry has the EOQ bit set in the command halfword and the end of the

transfer is reached. The EOQF bit remains set until cleared by writing a 1 to it. When the EOQF bit is set,

the TXRXS bit is automatically cleared.

0 EOQ is not set in the executing command.

1 EOQ is set in the executing SPI command.

27

TFUF

Transmit FIFO Underflow Flag

Indicates an underflow condition in the TX FIFO. The transmit underflow condition is detected only for SPI

blocks operating in Slave mode and SPI configuration. TFUF is set when the TX FIFO of the module

operating in SPI Slave mode is empty and an external SPI master initiates a transfer. The TFUF bit

remains set until cleared by writing 1 to it.

0 No TX FIFO underflow.

1 TX FIFO underflow has occurred.

26

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

25

TFFF

Transmit FIFO Fill Flag

Provides a method for the module to request more entries to be added to the TX FIFO. The TFFF bit is set

while the TX FIFO is not full. The TFFF bit can be cleared by writing 1 to it or by acknowledgement from

the DMA controller to the TX FIFO full request.

NOTE:

The reset value of this bit is 0 when the module is disabled,(MCR[MDIS]=1).

0 TX FIFO is full.

1 TX FIFO is not full.

24

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

23

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

22

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

21

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

20

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

19

RFOF

Receive FIFO Overflow Flag

Indicates an overflow condition in the RX FIFO. The field is set when the RX FIFO and shift register are

full and a transfer is initiated. The bit remains set until it is cleared by writing a 1 to it.

0 No Rx FIFO overflow.

1 Rx FIFO overflow has occurred.

Table continues on the next page...

Chapter 45 Serial Peripheral Interface (SPI)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1143

Loading...

Loading...